Other Parts Discussed in Thread: DRA716

Tool/software:

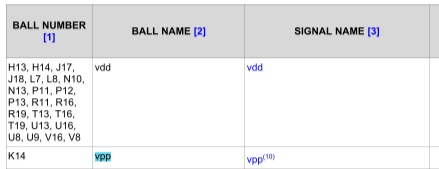

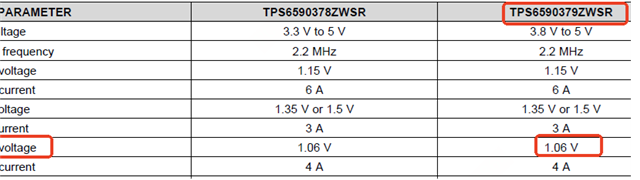

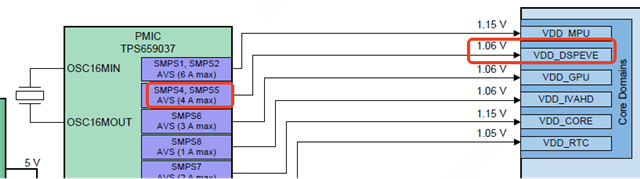

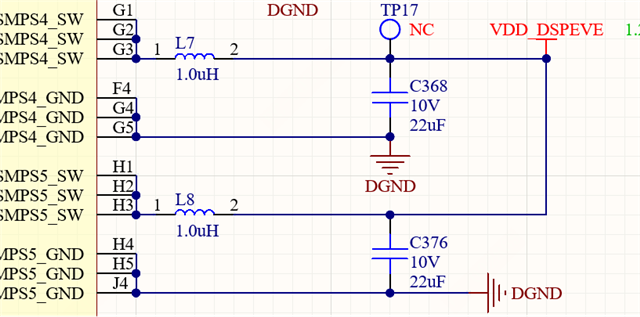

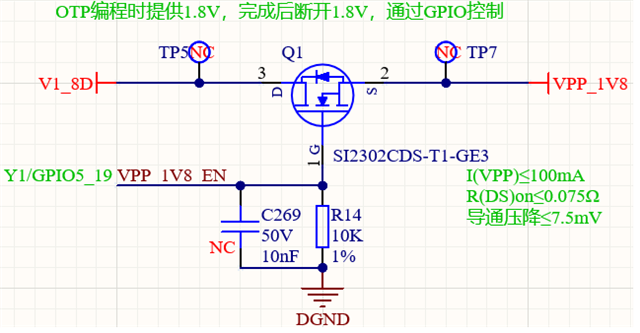

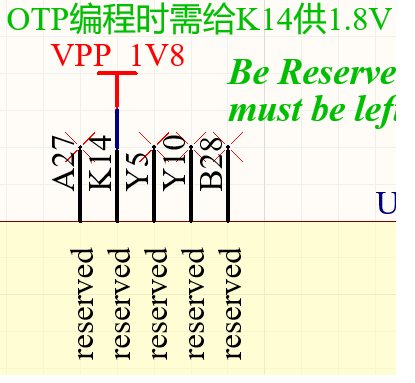

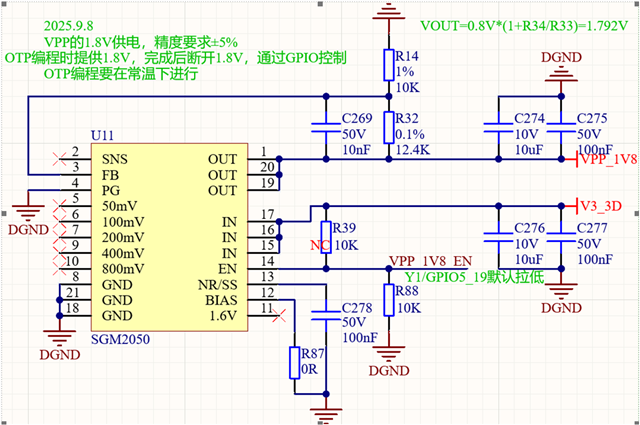

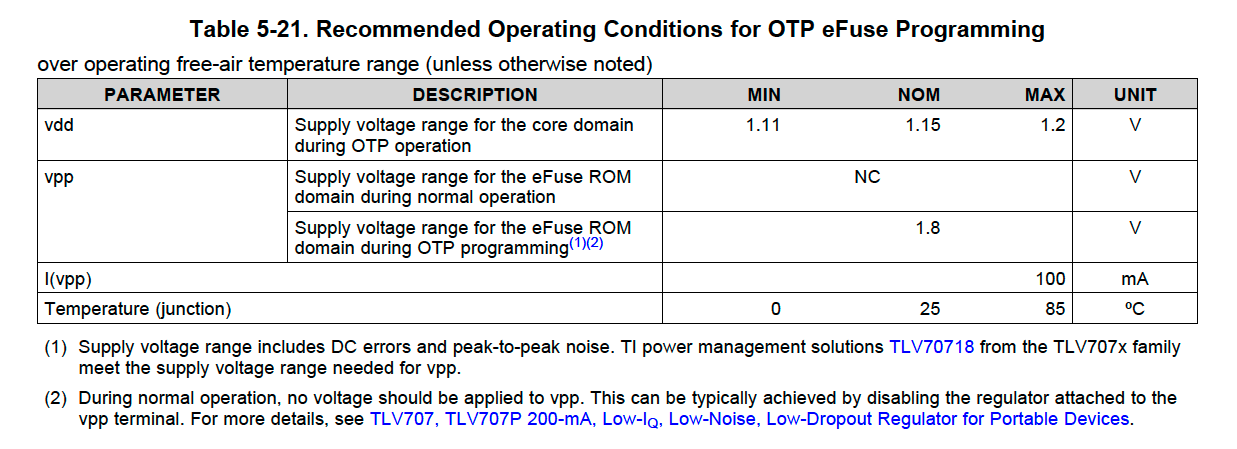

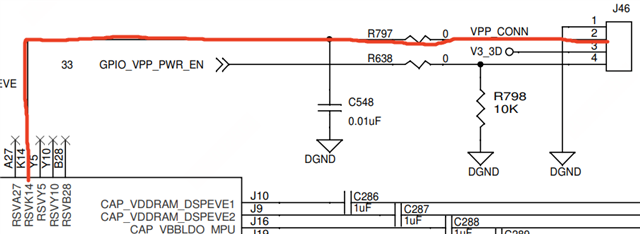

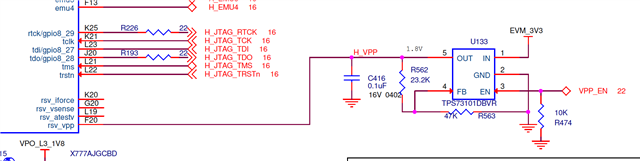

使用TLV70718还需要新增一个器件,我们想使用已有的TPS6590379ZWSR来给VPP供电,该怎样实现?

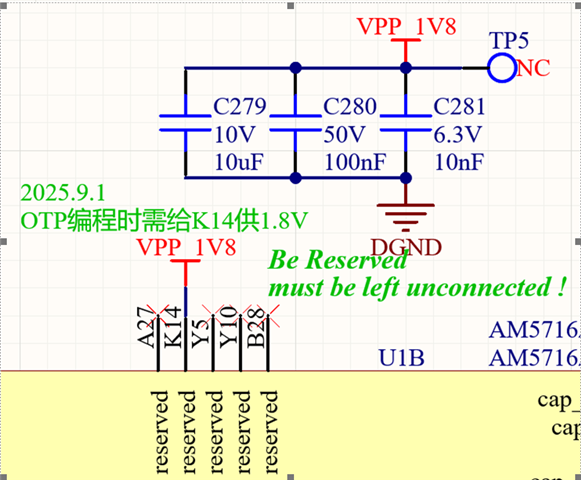

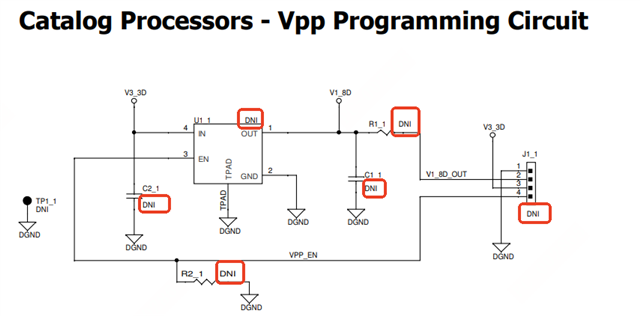

in the security boot document, it recommends customer to use TLV70718 to provide VPP power, but in customer design of AM5716 HW board,

there is no such device, if add a new TLV70718 device, it needs customer to re-design the HW, this is a big change,

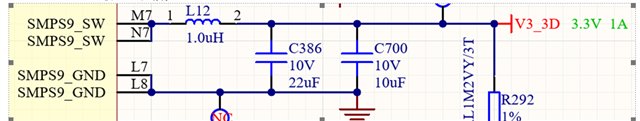

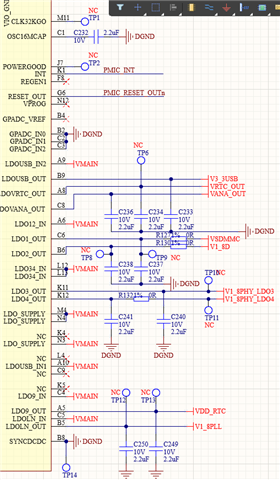

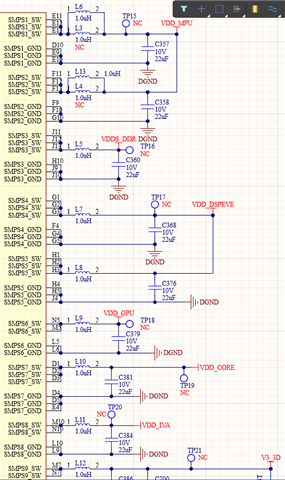

in customer AM5716 GP board, it use TPS6590379ZWSR as power supply solution,

is it possible customer to use TPS6590379ZWSR to provide power to VPP?

please help check it.

Thanks

Semon

\

\