Tool/software:

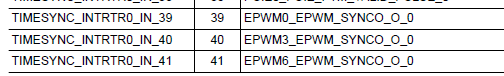

I’m trying to understand how to set up a connection for a synchronization signal between EPWM and PRU. The goal is to trigger the PRU Task Manager at the zero-crossing point of the EPWM, similar to what appears to be done in the SDFM example. I want the sync signal to reset the IEP counter, which then generates a CMP event at the zero-crossing and at other defined counter values.

However, I couldn’t find any TSR configuration in that example.

A few questions I’m hoping to clarify:

- Is the recommended approach to configure TSR via direct register writes from PRU, or should this be handled through SYSFW?

- If SYSFW is involved, is there an example or documentation showing how to define these interrupt routes in the resource configuration?

- The R5F core should be initialized from Linux. The R5F then initialize the PRU. The RPU sets the required resources or should it be done by R5F?

Best regards,

Niklas Haase