Other Parts Discussed in Thread: TPS65910, TPS82130

Tool/software:

Hi Expert,

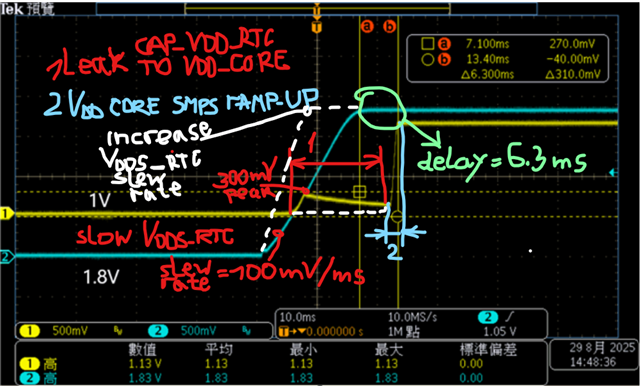

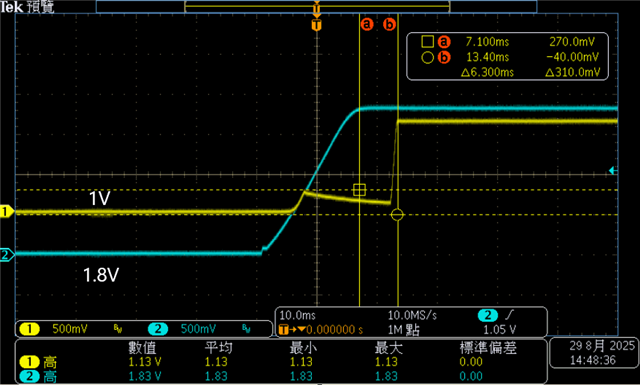

When conducting electrical measurements on the AM3352, it was discovered that the 1.1V power supply of the AM3352 had a leakage problem.

It was confirmed that the 1.8V power supply leaked to the 1.1V_Core power supply. The power sequence requirement in the datasheet is that 1.8V must rise before 1.1V.

According to the datasheet, there's a slight current leakage (surge) at 1.1V when the 1.8V voltage rises. Does this current leakage (surge) have any impact? Is there any solution?

Thanks

Daniel