Other Parts Discussed in Thread: AM625, SK-AM62P-LP, SN74AHC1G08, SN74AHC1G09, AM62P, AM62L, TCAN1043-Q1, TMDS64EVM, TCAN1043, SK-AM62-LP, TPS65988

Tool/software:

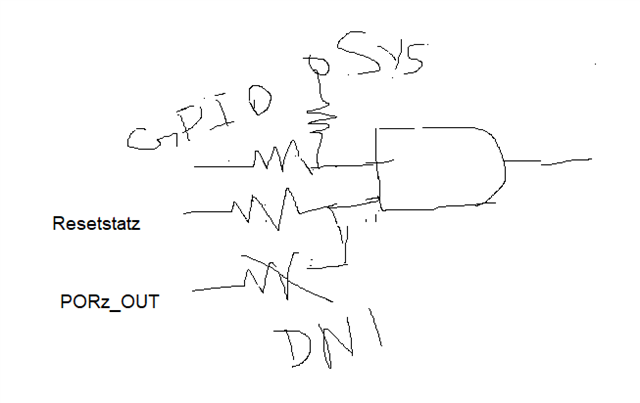

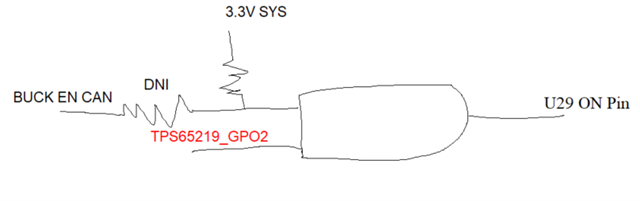

1) We are using the AM620-Q1 EVM reference schematic in our design. In this schematic, there is a net named “VPP_LDO_EN” which was previously controlled by the I/O expander externally. Now we are not using the I/O expander, where should this signal be connected?

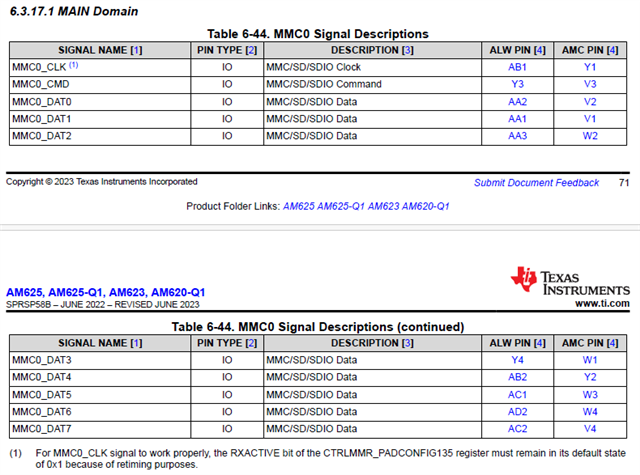

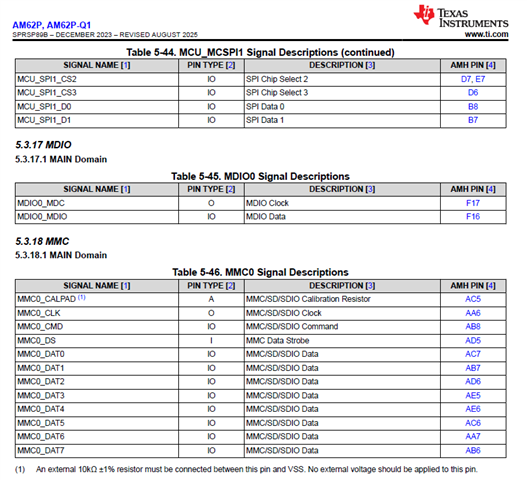

2) We are using the PSE2A0SL-08GX eMMC. This eMMC includes a Data Strobe (DS) pin. Currently, we have connected the DS pin to the W18 pin of the SoC (since it is a free pin, as we are using only a single Ethernet channel). Is this the correct connection? If not, please suggest the proper pin to which it should be connected.