Tool/software:

Hi:

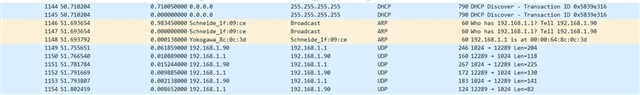

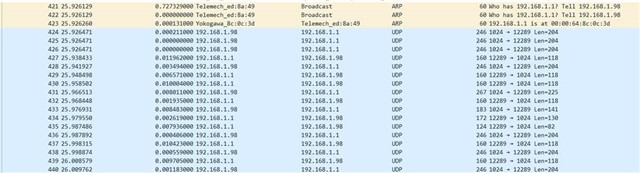

1) When our device communicates with a PLC through a network port, there is no problem with normal communication. However, if the network cable is unplugged or the PLC is powered off, and we wait for about a minute to restore it, the communication packet between the device and the PLC will be disrupted;

2) There are two messages in the attachment, one is the message that other products and this PLC can recover normally (GP4000), and the other is the message that our product and this PLC cannot recover normally after communication is restored. (192.168.1.1 corresponds to the address of the PLC, and the upper layer application processing of the two products uses the same WindRiver vxworks system, only the lower layer CPU is different)

3) From the confused messages, it can be seen that when reconnecting, the HMI sent three consecutive messages to the PLC with almost no time interval, and the subsequent PLC replies were confused.

I would like to know if there are any relevant configurations for the network port driver to not send cached messages when the link is disconnected in response to this situation,I have attached the code file for our current network port driver in the attachment.

/* vxbCpswEnd.c - TI 3 port gigabit switch VxBus END driver */

/*

* Copyright (c) 2011-2016 Wind River Systems, Inc.

*

* The right to copy, distribute, modify or otherwise make use

* of this software may be licensed only pursuant to the terms

* of an applicable Wind River license agreement.

*/

/*

DESCRIPTION

This module implements an END driver for the TI 3 port gigabit switch

(CPSW) network interface. The TI CPSW is a layer 2 ethernet switch.

The TI CPSW combines two(maybe more in future) 10/100/1000 MAC ports

and a CPU(host) port.

This driver doesn't support CPSW operating in switch mode. It will

configure the CPSW to operate in independent port mode by disabling

address learning on the all GMAC ports and constructing the MAC address

look-up table manually during intialization.

To VxBus, each cpsw port will has a device instance and each port has

private device contexts. Also each port can be loaded/unloaded independently.

This driver supports promisc mode by setting ALE (Address Lookup Engine)

into bypass mode. In bypass mode, all packets received will be forwarded

only to host port and ingress checking is ignored. Because there are two

ethernet port inside the CPSW, so there are two END objects showing up

when calling ifconfig shell command and because ALE is a shared resouce

so if one port is put into promisc mode then the other will also be put

into promisc mode automatically, but interface capability flags don't change

automactically. For example, calling:

\cs

ifconfig "cpsw0 inet promisc"

\ce

will put both cpsw0 and cpsw1 into promisc mode, but only cpsw0's

capability flags will show:

\cs

UP RUNNING SIMPLEX BROADCAST MULTICAST PROMISC ALLMULTI

\ce

cpsw1's capability flags will not be changed, the following command

must be called for cpsw1 to show up correctly:

\cs

ifconfig "cpsw1 inet promisc"

\ce

This same is true when removing promisc mode.

BOARD LAYOUT

The network interfaces are internal to the CPU. All configurations

are jumperless. See target.ref for connector locations.

EXTERNAL INTERFACE

The driver provides the standard VxBus external interface,

vxbCpswEndRegister(). This function registers the driver with the VxBus

subsystem, and instances will be created as needed. Since this is

a processor local bus device, each device instance must be specified

in the hwconf.c file in a BSP. The hwconf entry must specify the following

parameters (NOTE: this driver does require many sub-module register offset

specified as the offfset may be different on other boards, eg.

on TI DM647/DM648 the offset of various sub-modules and port number

assignments are different from this one):

\is

\i <cpswBase>

Specifies the base address where Network control module registers are mapped

into the host's address space. All register offsets are computed relative to

this address

\i <portOffset>

Specifies the offset of host port register set.

\i <cpdmaOffset>

Specifies the offset of DMA register set.

\i <statsOffset>

Specifies the offset of statictics register set.

\i <aleOffset>

Specifies the offset of ALE register set.

\i <mdioOffset>

Specifies the offset of MDIO register set.

\i <wrOffset>

Specifies the offset of WR register set.

\i <cpdmaHdpOffset>

Specifies the offset of CPDMA register set.

\i <workMode>

Specifies word mode of cpsw, only independent port is supportted.

\i <sysGetChipVer>

Speficies the function that returns SoC chip version. This

information is used to set different features of different SoC.

\i <phyAddr>

Specifies the phy address of port.

\i <portIndex>

Specifies the port index of port, the CPU(host) port which connects

to CPU is 0, other ports start from 1.

\i <portOffset>

Specifies the offset of PORT register set.

\i <gmacOffset>

Specifies the offset of GMAC register set.

\i <switchData>

Specifies the address of switch common resource, all the ports share

same switchData.

\ie

An example hwconf entry is shown below:

\cs

LOCAL CPSW_SWITCH_DATA cpswSwitchData = {

AM335X_EMAC0_BASE , /@ cpswBase @/

0x108 , /@ portOffset @/

0x800 , /@ cpdmaOffset @/

0x900 , /@ statsOffset @/

0xd00 , /@ aleOffset @/

0x1000 , /@ mdioOffset @/

0x1200 , /@ wrOffset @/

0x200 , /@ cpdmaHdpOffset @/

CPSW_MODE_INDEPENDENT_PORT , /@ work mode @/

sysGetChipVer , /@ chipVersion function @/

};

struct hcfResource am335xCpsw0Resources[] = {

{ "phyAddr", HCF_RES_INT, {(void *)0} },

{ "portIndex", HCF_RES_INT, {(void *)1} },

{ "portOffset", HCF_RES_INT, {(void *)0x208} },

{ "gmacOffset", HCF_RES_INT, {(void *)0xd80} },

{ "switchData", HCF_RES_ADDR, {(void *)&cpswSwitchData} },

};

#define am335xCpsw0Num NELEMENTS(am335xCpsw0Resources)

struct hcfResource am335xCpsw1Resources[] = {

{ "phyAddr", HCF_RES_INT, {(void *)1} },

{ "portIndex", HCF_RES_INT, {(void *)2} },

{ "portOffset", HCF_RES_INT, {(void *)0x308} },

{ "gmacOffset", HCF_RES_INT, {(void *)0xdc0} },

{ "switchData", HCF_RES_ADDR, {(void *)&cpswSwitchData} },

};

#define am335xCpsw1Num NELEMENTS(am335xCpsw1Resources)

\ce

\cs

This driver requires one external support function from the BSP.

\ce

\is

\i sysNetMacNVRamAddrGet()

\ie

\cs

STATUS sysNetMacNVRamAddrGet (ifName, ifUnit, ifMacAddr, ifMacAddrLen)

\ce

\cs

This routine queries the BSP to provide the ethernet address for a given MAC.

\ce

Note: This driver only supports dual emac mode, switch mode is not supported.

RESTRICTIONS

SEE ALSO: VxBus, miiBus, ifLib

*/

#include <vxWorks.h>

#include <string.h>

#include <intLib.h>

#include <stdio.h>

#include <logLib.h>

#include <muxLib.h>

#include <netLib.h>

#include <netBufLib.h>

#include <semLib.h>

#include <sysLib.h>

#include <vxBusLib.h>

#include <wdLib.h>

#include <etherMultiLib.h>

#include <end.h>

#include "errno.h"

#define END_MACROS

#include <endLib.h>

#include <endMedia.h>

#include <cacheLib.h>

#include <spinLockLib.h>

#include <vxAtomicLib.h>

#include <hwif/vxbus/vxBus.h>

#include <hwif/vxbus/hwConf.h>

#include <hwif/util/vxbDmaBufLib.h>

#include <hwif/util/vxbParamSys.h>

#include <../src/hwif/h/mii/miiBus.h>

#include <../src/hwif/h/vxbus/vxbAccess.h>

#include <../src/hwif/h/hEnd/hEnd.h>

#include "vxbCpswEnd.h"

#include "errno.h"

#include "sysNet.h"

#include "Dp83822Phy.h"

#include "LanExtFilter.h"

#include "am335xEndDrv.h"

#undef CPSW_DBG

#ifdef CPSW_DBG

/* NOTE: to use kprintf, INCLUDE_DEBUG_KPRINTF should be included */

#include <private/kwriteLibP.h>

#define DBG_MSG(...) \

(*_func_kprintf)("%s,%d, ", __FUNCTION__, __LINE__); \

(*_func_kprintf)(__VA_ARGS__)

#else

#define DBG_MSG(...)

#endif /* CPSW_DBG */

#undef CPSWDRV_DEBUG

#ifdef CPSWDRV_DEBUG

#include "usrLib.h" /* d()-display memory */

#define CPSWDRV_DEBUG_OFF 0x0000

#define CPSWDRV_DEBUG_RX 0x0001

#define CPSWDRV_DEBUG_TX 0x0002

#define CPSWDRV_DEBUG_INT 0x0004

#define CPSWDRV_DEBUG_POLL (CPSWDRV_DEBUG_POLL_RX | CPSWDRV_DEBUG_POLL_TX)

#define CPSWDRV_DEBUG_POLL_RX 0x0008

#define CPSWDRV_DEBUG_POLL_TX 0x0010

#define CPSWDRV_DEBUG_LOAD 0x0020

#define CPSWDRV_DEBUG_IOCTL 0x0040

#define CPSWDRV_DEBUG_TRACE 0x0080

#define CPSWDRV_DEBUG_INFO 0x0100

#define CPSWDRV_DEBUG_DUMP 0x4000

#define CPSWDRV_DEBUG_ERROR 0x8000

int cpswDbg = 0xFFFF; /*CPSWDRV_DEBUG_OFF;*/

/* This one is specifically for use in the ISR */

#define CPSWDRV_LOGMSG(FLG, X0, X1, X2, X3, X4, X5, X6) \

do { \

if (cpswDbg & FLG) \

logMsg(X0, X1, X2, X3, X4, X5, X6); \

} while (0)

#else /* DRV_DEBUG */

#define CPSWDRV_LOGMSG(FLG, X0, X1, X2, X3, X4, X5, X6)

#endif /* DRV_DEBUG */

/* accessor definitions */

#define CPSW_BAR(pSwCtrl) pSwCtrl->cpswBase

#define CPSW_DMA_BAR(pSwCtrl) pSwCtrl->cpdmaOffset

#define ECSR_READ_4(pSwCtrl, addr) \

*(volatile UINT32 *)((UINT32)CPSW_BAR(pSwCtrl) + (addr))

#define ECSR_WRITE_4(pSwCtrl, addr, data) \

*(volatile UINT32 *)((UINT32)CPSW_BAR(pSwCtrl) + (addr)) = (data)

#define CSR_SET_BIT(pSwCtrl, offset, val) \

ECSR_WRITE_4(pSwCtrl, offset, ECSR_READ_4(pSwCtrl, offset) | (val))

#define CSR_CLR_BIT(pSwCtrl, offset, val) \

ECSR_WRITE_4(pSwCtrl, offset, ECSR_READ_4(pSwCtrl, offset) & ~(val))

/* DMA manipulation */

#define CPDMA_REG_READ(pSwCtrl, addr) \

*(volatile UINT32 *)((UINT32)CPSW_BAR(pSwCtrl) + \

(UINT32)CPSW_DMA_BAR(pSwCtrl) + (addr))

#define CPDMA_REG_WRITE(pSwCtrl, addr, data) \

*(volatile UINT32 *)((UINT32)CPSW_BAR(pSwCtrl) + \

(UINT32)CPSW_DMA_BAR(pSwCtrl) + (addr)) = (data)

#define CPDMA_TX_EN(pSwCtrl) \

ECSR_WRITE_4(pSwCtrl, CPSW_DMA_BAR(pSwCtrl) + CPDMA_TX_CONTROL, 0x1)

#define CPDMA_RX_EN(pSwCtrl) \

ECSR_WRITE_4(pSwCtrl, CPSW_DMA_BAR(pSwCtrl) + CPDMA_RX_CONTROL, 0x1)

#define CPDMA_RX_DIS(pSwCtrl) \

ECSR_WRITE_4(pSwCtrl, CPSW_DMA_BAR(pSwCtrl) + CPDMA_RX_CONTROL, 0x0)

#define CPDMA_TX_DIS(pSwCtrl) \

ECSR_WRITE_4(pSwCtrl, CPSW_DMA_BAR(pSwCtrl) + CPDMA_TX_CONTROL, 0x0)

LOCAL char * txChanErrMsg[] = { "NO error", "SOP errpr",

"Ownership bit not set in SOP buffer",

"Zero next buffer descriptor pointer without EOP",

"Zero buffer pointer", "Zero buffer length", "packet length error" };

LOCAL char * rxChanErrMsg[] = { "NO error", "reserved",

"Ownership bit not set in input buffer", "reserved",

"Zero buffer pointer", "Zero buffer on non-SOP descriptor",

"SOP buffer length not greater than offset" };

/* common resource which is shared by all port */

LOCAL CPSW_SW_CTRL *pSwCtrl = NULL;

LOCAL short G_cpsw0IpDetectPermission=0; /* 0: enable, 1:disable */

LOCAL short G_cpsw1IpDetectPermission=0; /* 0: enable, 1:disable */

LOCAL LanPktFilterF G_cpswIpdetect; /* Filter funtion */

SEM_ID GnSemId_cpswIpDetect = (SEM_ID) NULL; /* Semaphore for IP detect */

static BOOL gnLBTflag2 = FALSE; /* LoopBack Test flag */

#define CPSW_TIMEOUT 1000

/* import functions */

IMPORT FUNCPTR _func_m2PollStatsIfPoll;

IMPORT STATUS sysNetMacNVRamAddrGet(char *, int, UINT8 *, int);

IMPORT void sysUsDelay(int);

/* VxBus interfaces */

LOCAL void cpswInstInit( VXB_DEVICE_ID);

LOCAL void cpswInstInit2( VXB_DEVICE_ID);

LOCAL void cpswInstConnect( VXB_DEVICE_ID);

LOCAL STATUS cpswInstUnlink( VXB_DEVICE_ID, void *);

LOCAL void cpswMuxConnect( VXB_DEVICE_ID, void *);

STATUS cpswPhyRead( VXB_DEVICE_ID, UINT8, UINT8, UINT16 *);

STATUS cpswPhyWrite( VXB_DEVICE_ID, UINT8, UINT8, UINT16);

LOCAL STATUS cpswLinkUpdate( VXB_DEVICE_ID);

/* driver utility functions */

LOCAL struct drvBusFuncs cpswFuncs = { cpswInstInit, /* devInstanceInit */

cpswInstInit2, /* devInstanceInit2 */

cpswInstConnect /* devConnect */

};

LOCAL struct vxbDeviceMethod cpswMethods[] = {

DEVMETHOD(miiRead, cpswPhyRead),

DEVMETHOD(miiWrite, cpswPhyWrite),

DEVMETHOD(miiMediaUpdate,cpswLinkUpdate),

DEVMETHOD(muxDevConnect, cpswMuxConnect),

DEVMETHOD(vxbDrvUnlink, cpswInstUnlink), { 0, 0 } };

/* default queue parameters */

LOCAL HEND_RX_QUEUE_PARAM cpswRxQueueDefault = {

NULL, /* jobQueId */

0, /* priority */

0, /* rbdNum */

0, /* rbdTupleRatio */

0, /* rxBufSize */

NULL, /* pBufMemBase */

0, /* rxBufMemSize */

0, /* rxBufMemAttributes */

NULL, /* rxBufMemFreeMethod */

NULL, /* pRxBdBase */

0, /* rxBdMemSize */

0, /* rxBdMemAttributes */

NULL /* rxBdMemFreeMethod */

};

LOCAL HEND_TX_QUEUE_PARAM cpswTxQueueDefault = {

NULL, /* jobQueId */

0, /* priority */

0, /* tbdNum */

0, /* allowedFrags */

NULL, /* pTxBdBase */

0, /* txBdMemSize */

0, /* txBdMemAttributes */

NULL /* txBdMemFreeMethod */

};

LOCAL VXB_PARAMETERS cpswParamDefaults[] = { { "rxQueue00", VXB_PARAM_POINTER, {

(void *) &cpswRxQueueDefault } }, { "txQueue00", VXB_PARAM_POINTER, {

(void *) &cpswTxQueueDefault } }, { NULL, VXB_PARAM_END_OF_LIST,

{ NULL } } };

LOCAL struct vxbDevRegInfo cpswDevPlbRegistration = {

NULL, /* pNext */

VXB_DEVID_DEVICE, /* devID */

VXB_BUSID_PLB, /* busID = PLB */

VXB_VER_4_0_0, /* VxBus Version */

CPSW_NAME, /* drvName */

&cpswFuncs, /* pDrvBusFuncs */

cpswMethods, /* pMethods */

NULL, /* devProbe */

cpswParamDefaults /* pParamDefaults */

};

/* END functions */

END_OBJ *cpswEndLoad(char *, void *);

LOCAL STATUS cpswEndUnload(END_OBJ *);

LOCAL int cpswEndIoctl(END_OBJ *, int, caddr_t);

LOCAL STATUS cpswEndMCastAddrAdd(END_OBJ *, char *);

LOCAL STATUS cpswEndMCastAddrDel(END_OBJ *, char *);

LOCAL STATUS cpswEndMCastAddrGet(END_OBJ *, MULTI_TABLE *);

LOCAL STATUS cpswEndStart(END_OBJ *);

LOCAL STATUS cpswEndStop(END_OBJ *);

LOCAL int cpswEndEncap(CPSW_DRV_CTRL *, M_BLK_ID);

LOCAL int cpswEndSend(END_OBJ *, M_BLK_ID);

LOCAL STATUS cpswEndPollSend(END_OBJ *, M_BLK_ID);

LOCAL int cpswEndPollReceive(END_OBJ *, M_BLK_ID);

LOCAL void cpswEndRxHandle(void *);

LOCAL void cpswEndTxHandle(void *);

LOCAL void cpswEndMiscHandle(void *);

LOCAL STATUS cpswSwitchInit(CPSW_SWITCH_DATA *);

LOCAL STATUS cpswHostPortInit(CPSW_SW_CTRL *);

LOCAL STATUS cpswGmacPortInit(CPSW_DRV_CTRL *);

LOCAL void cpswEndTxInt(CPSW_SW_CTRL *);

LOCAL void cpswEndRxInt(CPSW_SW_CTRL *);

LOCAL void cpswEndMiscInt(CPSW_SW_CTRL *);

LOCAL STATUS cpswSoftReset(CPSW_SW_CTRL *, UINT32, UINT32);

LOCAL void cpswReset(VXB_DEVICE_ID pDev);

/* CPDMA routines */

LOCAL STATUS cpswDmaInit(CPSW_SW_CTRL *);

LOCAL STATUS cpswDmaChanRequest(CPSW_SW_CTRL *, BOOL, int);

LOCAL STATUS cpswDmaChanRelease(CPSW_SW_CTRL *, BOOL, int);

/* ALE routines */

LOCAL int cpswAleAddMultiCast(CPSW_SW_CTRL *, unsigned char *, int, int, int,

int);

LOCAL int cpswAleAddUniCast(CPSW_SW_CTRL *, unsigned char *, int, int, int, int);

LOCAL void cpswAleRead(CPSW_SW_CTRL *, CPSW_ALE_TBL *, UINT32);

LOCAL void cpswAleWrite(CPSW_SW_CTRL *, CPSW_ALE_TBL *, UINT32);

LOCAL int cpswAleFind(CPSW_SW_CTRL *);

LOCAL int cpswAleMatch(CPSW_SW_CTRL *, unsigned char *);

LOCAL int cpswAleMatchVlan(CPSW_SW_CTRL *, int);

LOCAL int cpswAleAddVlan(CPSW_SW_CTRL *, int, int, int, int, int);

void cpswAleEntryShow(CPSW_ALE_TBL *);

void cpswAleDump(void);

LOCAL NET_FUNCS cpswNetFuncs = { cpswEndStart, /* start func. */

cpswEndStop, /* stop func. */

cpswEndUnload, /* unload func. */

cpswEndIoctl, /* ioctl func. */

cpswEndSend, /* send func. */

cpswEndMCastAddrAdd, /* multicast add func. */

cpswEndMCastAddrDel, /* multicast delete func. */

cpswEndMCastAddrGet, /* multicast get fun. */

cpswEndPollSend, /* cpswPolling send func. */

cpswEndPollReceive, /* cpswPolling receive func. */

endEtherAddressForm, /* put address info into a NET_BUFFER */

endEtherPacketDataGet, /* get pointer to data in NET_BUFFER */

endEtherPacketAddrGet /* Get packet addresses */

};

/********************************************************************************

* cpswWriteMac - write mac address.

*

* This function write MAC address to the serial flush NOR.

*

* RETURNS: OK/ERROR

********************************************************************************/

STATUS cpswWriteMac(UINT8 *pBuf, int ifUnit) /* bffer for mac address */ {

/* In Kernel side, it does not allow to write MAC address */

/* This function is used for developer */

if((ifUnit == 0)||(ifUnit ==1))

{

return sysNetMacAddrSet("cpsw", ifUnit, pBuf,CPSW_SFN_MAC_DATA_LEN);

}

else

{

return ERROR;

}

}

/********************************************************************************

* cpswReadMac - read mac address.

*

* This function read MAC address from the serial flush NOR.

*

* RETURNS: OK/ERROR

********************************************************************************/

STATUS cpswReadMac(UINT8 *pBuf,int ifUnit /* (o) read buffer for MAC address */

)

{

if((ifUnit == 0)||(ifUnit ==1))

{

return sysEnetAddrGet(ifUnit, pBuf);

}

else

{

return ERROR;

}

}

/********************************************************************************

* STATUS cpswCheckSum - check serial flush NOR checksum.

*

* This function checks the checksum in the serial flush NOR.

*

* RETURNS: OK/ERROR

********************************************************************************/

STATUS cpswCheckSum(int ifUnit) {

UINT8 buf[MAC_ADRS_LEN];

if (cpswReadMac(buf, ifUnit)) {

return (ERROR);

} else {

return (OK);

}

}

/*****************************************************************************

*

* cpswReset - reset the controller

*

* This function issues a reset command to the controller and waits

* for it to complete. This routine is always used to place the

* controller into a known state prior to configuration.

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL void cpswReset(VXB_DEVICE_ID pDev) {

CPSW_DRV_CTRL *pDrvCtrl = pDev->pDrvCtrl;

/* Reset the CPSW */

cpswSoftReset(pSwCtrl, CPSW_SOFT_RESET, CPSW_TIMEOUT_VAL);

cpswSoftReset(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_SOFT_RESET,CPSW_TIMEOUT_VAL);

cpswSoftReset(pSwCtrl, CPSW_WR_SOFTRESET, CPSW_TIMEOUT_VAL);

cpswSoftReset(pSwCtrl, pSwCtrl->cpdmaOffset + CPDMA_SOFT_RESET, CPSW_TIMEOUT_VAL);

}

/*******************************************************************************

* cpswEndPollStart - start polled mode operations

*

* RETURNS: OK only.

*******************************************************************************/

STATUS cpswEndPollStart(CPSW_DRV_CTRL *pDrvCtrl /* device to be initialized */

) {

pDrvCtrl->cpswPolling = TRUE;

/* stop tx dma channel interrupt */

CPDMA_REG_WRITE(pSwCtrl, CPDMA_TX_INTMASK_CLR,

BIT(pDrvCtrl->cpswTxDmaChan));

CSR_CLR_BIT(pSwCtrl, pSwCtrl->wrOffset + CPSW_WR_C0_TX_EN,

BIT(pDrvCtrl->cpswTxDmaChan));

/* stop rx dma channel interrupt */

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_INTMASK_CLR,

BIT(pDrvCtrl->cpswRxDmaChan));

CSR_CLR_BIT(pSwCtrl, pSwCtrl->wrOffset + CPSW_WR_C0_RX_EN,

BIT(pDrvCtrl->cpswRxDmaChan));

/*

* We may have been asked to enter polled mode while there are

* transmissions pending. This is a problem, because the polled

* transmit routine expects that the TX ring will be empty when

* it's called. In order to guarantee this, we have to drain

* the TX ring here. We could also just plain reset and

* reinitialize the transmitter, but this is faster.

*/

while (pDrvCtrl->cpswTxFree < CPSW_DESC_CNT) {

M_BLK_ID pMblk;

volatile CPSW_DESC *desc;

desc = &pDrvCtrl->cpswTxDescMem[pDrvCtrl->cpswTxQHead];

if (desc->flags & CPSW_EOQ) {

ECSR_WRITE_4(pSwCtrl, CPDMA_TX_CP(pDrvCtrl->cpswTxDmaChan),

desc->phys);

if (desc->link) {

ECSR_WRITE_4(pSwCtrl, CPDMA_TX_HDP(pDrvCtrl->cpswTxDmaChan),

desc->link);

}

}

while (desc->flags & CPSW_OWNERSHIP)

;

pMblk = pDrvCtrl->cpswTxblk[pDrvCtrl->cpswTxQHead];

if (pMblk != NULL) {

endPoolTupleFree(pMblk);

pDrvCtrl->cpswTxblk[pDrvCtrl->cpswTxQHead] = NULL;

}

pDrvCtrl->cpswTxFree++;

CPSW_DESC_INC(pDrvCtrl->cpswTxQHead, CPSW_DESC_CNT);

}

return ( OK);

}

/*******************************************************************************

* cpswEndPollStop - start polled mode operations

*

* This function start polling mode.

*

* RETURNS: OK only.

*******************************************************************************/

STATUS cpswEndPollStop(CPSW_DRV_CTRL *pDrvCtrl /* device to be initialized */

) {

pDrvCtrl->cpswPolling = FALSE;

/* enable relative tx channel interrupts */

CPDMA_REG_WRITE(pSwCtrl, CPDMA_TX_INTMASK_SET,

BIT(pDrvCtrl->cpswTxDmaChan));

CSR_SET_BIT(pSwCtrl, pSwCtrl->wrOffset + CPSW_WR_C0_TX_EN,

BIT(pDrvCtrl->cpswTxDmaChan));

/* enable relative rx channel interrupts */

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_INTMASK_SET,

BIT(pDrvCtrl->cpswRxDmaChan));

CSR_SET_BIT(pSwCtrl, pSwCtrl->wrOffset + CPSW_WR_C0_RX_EN,

BIT(pDrvCtrl->cpswRxDmaChan));

return ( OK);

}

/********************************************************************************

* STATUS cpswProcLbTest - LoopBack mode test

*

* This function tests the sending and receiving of the packet in the loop back mode.

*

* RETURNS: OK/ERROR

********************************************************************************/

STATUS cpswProcLbTest(CPSW_DRV_CTRL *pDrvCtrl){

int Loop1, Loop2;

M_BLK_ID pMblk= NULL;

M_BLK_ID pRMblk= NULL;

char *SendTestData = NULL;

int rtnVal = OK;

STATUS result;

if (pDrvCtrl == NULL)

{

return (ERROR);

}

SendTestData = malloc(CPSW_LPBK_TEST_LEN);

if (SendTestData == NULL) {

rtnVal = ERROR;

return (rtnVal);

}

/********************************

* create send data. Data length is CPSW_LPBK_TEST_LEN(default 1514).

* Sending data is flowing :

* [dist address]

* 0xff 0xff 0xff 0xff 0xff 0xff

*

* [source address]

* 0x06 0x07 0x08 0x09 0x0a 0x0b

*

* [length type field]

* 0x00 0x00

*

* [data field]

* 0xa5 0xa5 ............

********************************/

/* set distination address */

for (Loop1 = 0; Loop1 < 6; Loop1++) {

SendTestData[Loop1] = (UINT8) 0xFF;

}

/* set source address */

for (Loop1 = 6; Loop1 < 12; Loop1++) {

SendTestData[Loop1] = Loop1;

}

/*Set length type field */

SendTestData[12] = 0x00;

SendTestData[13] = 0x00;

/* fill data field */

for (Loop1 = 14; Loop1 < CPSW_LPBK_TEST_LEN; Loop1++) {

SendTestData[Loop1] = CPSW_LPBK_TEST_DAT;

}

cpswEndPollStart(pDrvCtrl);

/* if Rx Descritpor not empty */

if (vxAtomicCas(&pDrvCtrl->cpswRxIntPend, FALSE, TRUE) == TRUE) {

/* post the rx done job to task */

(void) jobQueuePost(pDrvCtrl->cpswJobQueue, &pDrvCtrl->cpswRxQJob);

}

/* Copy data from DMA buffer to the cluster */

pMblk = endPoolTupleGet(pDrvCtrl->cpswEndObj.pNetPool);

if (pMblk == NULL) {

rtnVal = ERROR;

logMsg("fail to get buffer\n", 0, 0, 0, 0, 0, 0);

goto error;

}

pMblk->mBlkHdr.mData = SendTestData;

pMblk->mBlkHdr.mLen = CPSW_LPBK_TEST_LEN;

pMblk->mBlkHdr.mFlags |= (M_PKTHDR | M_EXT);

pMblk->mBlkPktHdr.len = CPSW_LPBK_TEST_LEN;

pRMblk = endPoolTupleGet(pDrvCtrl->cpswEndObj.pNetPool);

if (pRMblk == NULL) {

rtnVal = ERROR;

goto error;

}

pRMblk->mBlkHdr.mFlags |= M_EXT;

pRMblk->m_len = pRMblk->m_pkthdr.len = CPSW_CLSIZE;

pRMblk->m_next = NULL;

for (Loop1 = 0; Loop1 < CPSW_LPBK_TEST_CNT; Loop1++) {

gnLBTflag2 = TRUE;

/* send data */

result = cpswEndPollSend(&pDrvCtrl->cpswEndObj, pMblk);

gnLBTflag2 = FALSE;

if ((result != OK) || (pMblk->mBlkHdr.mLen != CPSW_LPBK_TEST_LEN)) {

CPSWDRV_LOGMSG(CPSWDRV_DEBUG_ERROR,

"(:%d) Error cpswEndPollSend() ...\n", __LINE__, 2, 3, 4, 5,

6);

logMsg("fail to sendpi \n", 0, 0, 0, 0, 0, 0);

rtnVal = ERROR;

break;

}

sysUsDelay(500);

/* recv data */

result = cpswEndPollReceive(&pDrvCtrl->cpswEndObj, pRMblk);

if ((result != OK) || (pRMblk->mBlkHdr.mLen != CPSW_LPBK_TEST_LEN)) {

CPSWDRV_LOGMSG(CPSWDRV_DEBUG_ERROR,

"(:%d) Error cpswEndPollReceive() ...\n", __LINE__, 2, 3, 4,

5, 6);

rtnVal = ERROR;

logMsg("fail to recieve \n", 0, 0, 0, 0, 0, 0);

break;

}

/* check data */

for (Loop2 = 0; Loop2 < CPSW_LPBK_TEST_LEN; Loop2++) {

if (SendTestData[Loop2] != pRMblk->mBlkHdr.mData[Loop2]) {

logMsg("CPSWDRV_DEBUG_Error [%d]: S:0x%02x R:0x%02x\n", Loop2,

(UINT8) SendTestData[Loop2],

(UINT8) pRMblk->mBlkHdr.mData[Loop2], 0, 0, 0);

#ifdef CPSWDRV_DEBUG

if (cpswDbg != 0) {

d(SendTestData, 128, 1);

d(pRMblk->mBlkHdr.mData, 128, 1);

}

#endif

break;

}

}

CPSWDRV_LOGMSG(CPSWDRV_DEBUG_POLL, "%d done ok\n", Loop2, 2, 3, 4, 5,

6);

if (Loop2 < CPSW_LPBK_TEST_LEN) {

CPSWDRV_LOGMSG(CPSWDRV_DEBUG_ERROR,

"(:%d) Error data miss match(%d byte) ...\n", __LINE__,

Loop2, 3, 4, 5, 6);

logMsg("Error data miss matchr\n", 0, 0, 0, 0, 0, 0);

rtnVal = ERROR;

break;

}

}

error:

/* free Mblk */

if (pRMblk != NULL)

netMblkClChainFree(pRMblk);

if (pMblk != NULL)

netMblkClChainFree(pMblk);

cpswEndPollStop(pDrvCtrl);

free(SendTestData);

SendTestData=NULL;

return (rtnVal);

}

/********************************************************************************

* STATUS cpswTestLoopBack - LoopBack mode test

*

* This function tests the sending and receiving of the packet in the loop back mode.

*

* RETURNS: OK/ERROR

********************************************************************************/

STATUS cpswTestLoopBack(int ifUnit) {

CPSW_DRV_CTRL *pDrvCtrl =NULL;

UINT32 miiPhyFlags_saved, ctl_retval;

int rtnresult = 0;

UINT32 val;

if(ifUnit == 0)

{

pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME, CPSW_DEV_UNIT_NUM0);

}

else if(ifUnit == 1)

{

pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME, CPSW_DEV_UNIT_NUM1);

}

else

{

return ( ERROR);

}

if (pDrvCtrl == NULL) {

DBG_MSG ("Please run muxDevLoad.\n");

return ( ERROR);

}

if (!(pDrvCtrl->cpswEndObj.flags & IFF_UP))

return (ERROR);

/* save configuration */

cpswPhyRead(pDrvCtrl->pDev, (UINT8)pDrvCtrl->cpswPhyAddr, (UINT8)MII_CTRL_REG,(UINT16 *)&ctl_retval);

miiPhyFlags_saved = ctl_retval;

/* set loopback mode with 100base full-duplex */

if ((pDrvCtrl->cpswEndObj.flags & IFF_UP)== IFF_UP ) {

cpswEndStop(&pDrvCtrl->cpswEndObj);

}

/* pDrvCtrl->cpswMiiBus.flags = CPSW_USR_MII_100MB | CPSW_USR_MII_FD;*/

cpswEndStart(&pDrvCtrl->cpswEndObj);

cpswPhyWrite(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr, MII_CTRL_REG,

MII_CR_LOOPBACK | MII_CR_100 | MII_CR_FDX);

val = ECSR_READ_4(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_CTL);

val &= ~CPSW_EXT_EN;

val |= (CPSW_RMII_EN_100 | GMAC_CTL_FULLDUPLEX);

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_CTL, val);

/* run loopback test */

/* add loopback setting */

{

UINT16 retval;

{

cpswPhyRead(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr,

MII_PHY_BISTCNT_REG_DP83822, &retval);

retval &= (~MII_PHY_BIST_LOOPBACKMODE_MASK);

retval |= (MII_PHY_BIST_TRANMIILOOPBACK_bit

| MII_PHY_BIST_LOOPBACKMODE_DIGITAL);

cpswPhyWrite(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr,

MII_PHY_BISTCNT_REG_DP83822, retval);

}

}

rtnresult = cpswProcLbTest(pDrvCtrl);

/* del loopback setting */

{

UINT16 retval;

{ /* DP83822 */

cpswPhyRead(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr,

MII_PHY_BISTCNT_REG_DP83822, &retval);

retval &= (~(MII_PHY_BIST_TRANMIILOOPBACK_bit

| MII_PHY_BIST_LOOPBACKMODE_MASK));

cpswPhyWrite(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr,

MII_PHY_BISTCNT_REG_DP83822, retval);

cpswPhyRead(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr,

MII_PHY_BISTCNT_REG_DP83822, &retval); /* Dummy read for writing */

}

}

/* restore configuration */

cpswEndStop(&pDrvCtrl->cpswEndObj);

cpswPhyWrite(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr, MII_CTRL_REG,

miiPhyFlags_saved);

cpswEndStart(&pDrvCtrl->cpswEndObj);

return (rtnresult);

}

/******************************************************************************

* cpswGetLinkStat - get cable link status

*

* This function get LAN cable link status.

*

* RETURNS: ON(1) or OFF(0)

******************************************************************************/

int cpswGetLinkStat(int ifUnit) {

UINT16 regVal;

CPSW_DRV_CTRL *pDrvCtrl =NULL;

if(ifUnit == 0)

{

pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME,

CPSW_DEV_UNIT_NUM0);

}

else if(ifUnit == 1)

{

pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME,

CPSW_DEV_UNIT_NUM1);

}

else

{

return ( ERROR);

}

if (pDrvCtrl == NULL) {

DBG_MSG("Please run muxDevLoad.\n");

return (VxD_LANLINK_NG);

}

/* get PHY link stat */

if (cpswPhyRead(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr, MII_STAT_REG,

®Val) != OK) {

/* MII read error */

return (VxD_LANLINK_NG);

}

/* check link up stat */

if ((regVal & MII_SR_LINK_STATUS) == MII_SR_LINK_STATUS) {

/* cable is connected */

return (VxD_LANLINK_ON);

} else {

/* cable is unconnected */

return (VxD_LANLINK_OFF);

}

}

/******************************************************************************

* cpswGetLinkSpeed - get link speed

*

* This function get LAN link speed.

*

* RETURNS:

******************************************************************************/

int cpswGetLinkSpeed(int ifUnit) {

UINT16 regVal;

CPSW_DRV_CTRL *pDrvCtrl =NULL;

if(ifUnit == 0)

{

pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME,

CPSW_DEV_UNIT_NUM0);

}

else if(ifUnit == 1)

{

pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME,

CPSW_DEV_UNIT_NUM1);

}

else

{

return ( ERROR);

}

if (pDrvCtrl == NULL) {

return (LNKSPEED_10BASET_HALF);

}

cpswPhyRead(pDrvCtrl->pDev, pDrvCtrl->cpswPhyAddr, MII_PHY_STS_REG_DP83822,

®Val);

if ((regVal & MII_PHY_STS_SPEED_bit) == MII_PHY_STS_SPEED_bit) { /* 10Mbps */

if ((regVal & MII_PHY_STS_DUPLEX_bit) == MII_PHY_STS_DUPLEX_bit) { /* Full-Duplex */

return (LNKSPEED_10BASET_FULL);

} else { /* Half-Duplex */

return (LNKSPEED_10BASET_HALF);

}

} else { /* 100Mbps */

if ((regVal & MII_PHY_STS_DUPLEX_bit) == MII_PHY_STS_DUPLEX_bit) { /* Full-Duplex */

return (LNKSPEED_100BASETX_FULL);

} else { /* Half-Duplex */

return (LNKSPEED_100BASETX_HALF);

}

}

/* still in auto-negotiation : 10Base-T half-duplex */

return (LNKSPEED_10BASET_HALF);

}

/*******************************************************************************

* cpswSendDataDirect - the driver send routine

*

* This routine takes a M_BLK_ID sends off the data in the M_BLK_ID.

* The buffer must already have the addressing information properly installed

* in it. This is done by a higher layer.

*

* Please note that this procedure updates 'tmdLastIndex' and test 'tmdIndex'

*

* RETURNS: OK, ERROR or END_ERR_BLOCK when not enough descriptors are available.

*******************************************************************************/

/* This macro is convert virtual the address to physical address */

STATUS cpswSendDataDirect(CPSW_DRV_CTRL *pDrvCtrl, /* driver structure pointer */

char *pBuf, UINT32 len) {

CPSW_DRV_CTRL *pDev;

M_BLK_ID pMblk;

M_BLK_ID pTemp;

pDev = pDrvCtrl;

CPSW_DESC *head = NULL;

int i = 0;

if (pDev == NULL)

return (ERROR);

if (pDrvCtrl->cpswPolling == TRUE) {

return (ERROR);

}

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

END_TX_SEM_TAKE(&pDrvCtrl->cpswEndObj, WAIT_FOREVER);

if (!pDrvCtrl->cpswTxFree || !(pDrvCtrl->cpswEndObj.flags & IFF_UP))

goto blocked;

pMblk = endPoolTupleGet(pDrvCtrl->cpswEndObj.pNetPool);

if (pMblk == NULL) {

DBG_MSG("cpswSendDataDirect(:%d) (pMblk)blocked. \n", __LINE__);

goto blocked;

}

pMblk->mBlkHdr.mData = pBuf;

pMblk->mBlkHdr.mLen = pMblk->mBlkPktHdr.len=len;

pMblk->mBlkHdr.mFlags |= (M_PKTHDR | M_EXT);

if (cpswEndEncap(pDrvCtrl, pMblk) != OK) {

netMblkClChainFree (pMblk);

endPoolTupleFree(pMblk);

#if 0

END_TX_SEM_GIVE(&pDrvCtrl->cpswEndObj);

DBG_MSG("(:%d) cpswEndTxHandle cpswEndEncap Error!!! \n", __LINE__);

return (ERROR);

#else

goto blocked;

#endif

}

for (i = 0; i < CPSW_TIMEOUT_VAL; i++) {

if (CPDMA_REG_READ(pSwCtrl, CPDMA_TX_HDP(pDrvCtrl->cpswTxDmaChan))==0)

break;

}

if (i >= CPSW_TIMEOUT_VAL) {

goto blocked;

}

head = &pDrvCtrl->cpswTxDescMem[pDrvCtrl->cpswTxQHead];

pTemp = pDrvCtrl->cpswTxblk[pDrvCtrl->cpswTxQHead];

if (pTemp) {

pDrvCtrl->cpswTxblk[pDrvCtrl->cpswTxQHead] = NULL;

}

pDrvCtrl->cpswTxFree++;

CPDMA_REG_WRITE(pSwCtrl, CPDMA_TX_CP(pDrvCtrl->cpswTxDmaChan), head->phys);

CPSW_DESC_INC(pDrvCtrl->cpswTxQHead, CPSW_DESC_CNT);

END_TX_SEM_GIVE(&pDrvCtrl->cpswEndObj);

(void) semGive(pSwCtrl->cpswDevSem);

return (OK);

blocked:

pDrvCtrl->cpswTxstall = TRUE;

END_TX_SEM_GIVE(&pDrvCtrl->cpswEndObj);

(void) semGive(pSwCtrl->cpswDevSem);

DBG_MSG("(:%d) cpswSendDataDirect Error\n", __LINE__);

return (END_ERR_BLOCK);

}

/**********************************************************

* info : Send Direct function.

* arguments : char *Data

* pointer to send data.

* int Len

* send data length.

* return value : ERROR transmission fail.

* OK transmission success.

**********************************************************/

long cpswSendDirect_2(struct LanPktFilterST *Filter, char *Data, UINT32 Len,UINT16 sUnitNo) {

CPSW_DRV_CTRL *pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME, sUnitNo);

return cpswSendDataDirect(pDrvCtrl, Data, Len);

}

long cpswSendDirect(struct LanPktFilterST *Filter, char *Data, UINT32 Len) {

return cpswSendDirect_2(Filter, Data, Len,0);

}

/**********************************************************

* cpswEnableFilter - Regist/Unregist ip Direct function

*

* This function is Regist and Unregist the ip Direct functions.

* The Direct send function is registed cpswSendDirect.

* The Direct hook function is registed Arbitrary function.

*

* return value : OK, ERROR

**********************************************************/

UINT32 cpswEnableFilter_2(struct LanPktFilterST *Filter, UINT32 IsAdd,UINT16 sUnitNo ) {

CPSW_DRV_CTRL *pDrvCtrl = (CPSW_DRV_CTRL *) endFindByName(CPSW_NAME, sUnitNo);

if (IsAdd == 1) {

if (pDrvCtrl == NULL) {

DBG_MSG("Please run muxDevLoad.\n");

return (ERROR);

}

/* registration */

if (semTake(GnSemId_cpswIpDetect, WAIT_FOREVER) == ERROR) {

return (ERROR);

}

G_cpswIpdetect = Filter->PktFilterF; /* filter function */

if (semGive(GnSemId_cpswIpDetect) == ERROR) {

return (ERROR);

}

/* filled by LAN driver */

Filter->LocalAddr = (char *) pDrvCtrl->macaddr; /* MAC address */

Filter->PktSendF = cpswSendDirect_2; /* direct send function */

} else if (IsAdd == 0) {

/* unregistration */

if (semTake(GnSemId_cpswIpDetect, WAIT_FOREVER) == ERROR) {

return (ERROR);

}

G_cpswIpdetect = 0; /* filter function */

if (semGive(GnSemId_cpswIpDetect) == ERROR) {

return (ERROR);

}

/* cleared by LAN driver */

Filter->LocalAddr = 0; /* MAC address */

Filter->PktSendF = 0; /* direct send function */

} else {

/* IsAdd value error.*/

return (ERROR);

}

return (OK);

}

UINT32 cpswEnableFilter(struct LanPktFilterST *Filter, UINT32 IsAdd)

{

return cpswEnableFilter_2(Filter,IsAdd, 0);

}

/**********************************************************

* cpswCtrlNomSend - Send Direct function.

*

* This function control the normal sending.

*

* return value : OK only.

**********************************************************/

STATUS cpswCtrlNomSend_2(UINT32 option,INT16 sUnitNo) {

/* set enable/disable flag */

if( sUnitNo == 0 )

{

G_cpsw0IpDetectPermission = option;

}

else

{

G_cpsw1IpDetectPermission = option;

}

return (OK);

}

STATUS cpswCtrlNomSend(UINT32 option) {

/* set enable/disable flag */

G_cpsw0IpDetectPermission = option;

return (OK);

}

/******************************************************************************

*

* vxbCpswEndRegister - register with the VxBus subsystem

*

* This routine registers the CPSW driver with VxBus as a

* PLB bus type.

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

void vxbCpswEndRegister(void) {

vxbDevRegister((struct vxbDevRegInfo *) &cpswDevPlbRegistration);

}

/*******************************************************************************

*

* cpswInstInit - VxBus instInit handler

*

* This function implements the VxBus instInit handler for an CPSW

* device instance. The only thing done here is to select a unit

* number for the device.

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL void cpswInstInit(VXB_DEVICE_ID pDev) {

const struct hcfDevice *pHcf;

/* Always use the unit number allocated to us in the hwconf file. */

pHcf = hcfDeviceGet(pDev);

if (pHcf == NULL) {

return;

}

(void) vxbInstUnitSet(pDev, pHcf->devUnit);

}

/*******************************************************************************

*

* cpswInstInit2 - VxBus instInit2 handler

*

* This function implements the VxBus instInit2 handler for a CPSW

* device instance. Once we reach this stage of initialization, it's

* safe for us to allocate memory, so we can create our pDrvCtrl

* structure and do some initial hardware setup. The important

* steps we do here are to create a child miiBus instance, get the station

* address from the BSP, and set up our vxbDma tags and memory

* regions. We need to allocate a memory region for the RX DMA window

* here.

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL void cpswInstInit2(VXB_DEVICE_ID pDev) {

int cnt;

CPSW_DRV_CTRL *pDrvCtrl = NULL;

CPSW_SWITCH_DATA *pSwData;

const struct hcfDevice *pHcf = hcfDeviceGet(pDev);

if (pHcf == NULL) {

return;

}

/* get switch common resource info */

if (devResourceGet(pHcf, "switchData", HCF_RES_ADDR,

(void *) &pSwData) != OK) {

DBG_MSG("can not get pSwData resource\n");

goto failed;

}

if (cpswSwitchInit(pSwData) != OK) {

DBG_MSG("cpswSwitchInit() failed\n");

return;

}

pDrvCtrl = malloc(sizeof(CPSW_DRV_CTRL));

if (!pDrvCtrl) {

DBG_MSG("allocate pDrvCtrl failed\n");

goto failed;

}

memset(pDrvCtrl, 0, sizeof(CPSW_DRV_CTRL));

/* make connection between pDev and pDrvCtrl */

pDev->pDrvCtrl = pDrvCtrl;

pDrvCtrl->pDev = pDev;

/* make connection between pSwCtrl and pDrvCtrl */

pSwCtrl->port[pDev->unitNumber] = pDrvCtrl;

pDrvCtrl->pSwCtrl = pSwCtrl;

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

pSwCtrl->refCount++;

(void) semGive(pSwCtrl->cpswDevSem);

DBG_MSG("%s%d pSwCtrl->refCount = %d\n",

pDev->pName, pDev->unitNumber, pSwCtrl->refCount);

/* fetch parameter from bsp */

if (devResourceGet(pHcf, "phyAddr", HCF_RES_INT,

(void *) &pDrvCtrl->cpswPhyAddr) != OK) {

DBG_MSG("%s%d can not get phy address\n",

pDev->pName, pDev->unitNumber);

goto failed;

} DBG_MSG("%s%d get phy address: %d\n",

pDev->pName, pDev->unitNumber, pDrvCtrl->cpswPhyAddr);

if (devResourceGet(pHcf, "portIndex", HCF_RES_INT,

(void *) &pDrvCtrl->portIndex) != OK) {

DBG_MSG("%s%d can not get portIndex\n",

pDev->pName, pDev->unitNumber);

goto failed;

} DBG_MSG("%s%d get portIndex: %d\n",

pDev->pName, pDev->unitNumber, pDrvCtrl->portIndex);

if (devResourceGet(pHcf, "portOffset", HCF_RES_INT,

(void *) &pDrvCtrl->portOffset) != OK) {

DBG_MSG("%s%d can not get parameter portOffset\n",

pDev->pName, pDev->unitNumber);

goto failed;

} DBG_MSG("%s%d get parameter portOffset: 0x%08x\n",

pDev->pName, pDev->unitNumber, pDrvCtrl->portOffset);

if (devResourceGet(pHcf, "gmacOffset", HCF_RES_INT,

(void *) &pDrvCtrl->gmacOffset) != OK) {

DBG_MSG("%s%d can not get parameter gmacOffset\n",

pDev->pName, pDev->unitNumber);

goto failed;

} DBG_MSG("%s%d get parameter gmacOffset: 0x%08x\n",

pDev->pName, pDev->unitNumber, pDrvCtrl->gmacOffset);

/* allocating TX DMA buffer */

pDrvCtrl->cpswTxDescMem = cacheDmaMalloc(sizeof(CPSW_DESC) *

CPSW_DESC_CNT);

if (pDrvCtrl->cpswTxDescMem == NULL) {

DBG_MSG("%s%d can not create tx desc buffer\n",

pDev->pName, pDev->unitNumber);

goto failed;

}

memset(pDrvCtrl->cpswTxDescMem, 0, sizeof(CPSW_DESC) * CPSW_DESC_CNT);

for (cnt = 0; cnt < CPSW_DESC_CNT; cnt++) {

/* save the physical address into desc */

pDrvCtrl->cpswTxDescMem[cnt].phys =

(UINT32) &(pDrvCtrl->cpswTxDescMem[cnt]);

}

/* allocating RX DMA buffer */

pDrvCtrl->cpswRxDescMem = cacheDmaMalloc(sizeof(CPSW_DESC) *

CPSW_DESC_CNT);

if (!pDrvCtrl->cpswRxDescMem) {

DBG_MSG("%s%d can not create rx desc buffer\n",

pDev->pName, pDev->unitNumber);

goto failed;

}

memset(pDrvCtrl->cpswRxDescMem, 0, sizeof(CPSW_DESC) * CPSW_DESC_CNT);

for (cnt = 0; cnt < CPSW_DESC_CNT; cnt++) {

/* save the physical address into desc */

pDrvCtrl->cpswRxDescMem[cnt].phys =

(UINT32) &(pDrvCtrl->cpswRxDescMem[cnt]);

}

/* attach ISR */

vxbIntConnect(pDev, 0, cpswEndTxInt, pSwCtrl);

vxbIntConnect(pDev, 1, cpswEndRxInt, pSwCtrl);

vxbIntConnect(pDev, 2, cpswEndMiscInt, pSwCtrl);

/* create the MII bus */

if (miiBusCreate(pDev, &pDrvCtrl->cpswMiiBus) != OK) {

DBG_MSG("%s%d miiBusCreate() failed\n",

pDev->pName, pDev->unitNumber);

goto failed;

}

miiBusMediaListGet(pDrvCtrl->cpswMiiBus, &pDrvCtrl->cpswMediaList);

miiBusModeSet(pDrvCtrl->cpswMiiBus,

pDrvCtrl->cpswMediaList->endMediaListDefault);

return;

failed: if (pDrvCtrl) {

if (pDrvCtrl->cpswTxDescMem)

cacheDmaFree(pDrvCtrl->cpswTxDescMem);

if (pDrvCtrl->cpswRxDescMem)

cacheDmaFree(pDrvCtrl->cpswRxDescMem);

free(pDrvCtrl);

pDrvCtrl=NULL;

}

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

pSwCtrl->refCount--;

pSwCtrl->port[pDev->unitNumber] = NULL;

(void) semGive(pSwCtrl->cpswDevSem);

if (pSwCtrl->refCount == 0) {

(void) semDelete(pSwCtrl->cpswDevSem);

free(pSwCtrl);

pSwCtrl = NULL;

DBG_MSG("%s%d pSwCtrl is freed\n",

pDev->pName, pDev->unitNumber);

}

}

/*******************************************************************************

*

* cpswInstConnect - VxBus instConnect handler

*

* This function implements the VxBus instConnect handler for an CPSW

* device instance. This routine connects the CPSW ISR routines here.

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL void cpswInstConnect(VXB_DEVICE_ID pDev) {

return;

}

/*******************************************************************************

*

* cpswSwitchInit - initialize CPSW switch common resource

*

* This routine initializes the CPSW switch common resource.

*

* RETURNS: OK or ERROR if failed.

*

* ERRNO: N/A

*/

LOCAL STATUS cpswSwitchInit(CPSW_SWITCH_DATA *pSwData) {

FUNCPTR chipVerGetFunc;

/* check if switch common resource already been initialized */

if (pSwCtrl != NULL)

return OK;

pSwCtrl = malloc(sizeof(CPSW_SW_CTRL));

if (!pSwCtrl) {

DBG_MSG("malloc space for CPSW_SW_CTRL failed\n");

return ERROR;

}

memset(pSwCtrl, 0, sizeof(CPSW_SW_CTRL));

pSwCtrl->cpswBase = pSwData->cpswBase;

pSwCtrl->portOffset = pSwData->portOffset;

pSwCtrl->cpdmaOffset = pSwData->cpdmaOffset;

pSwCtrl->statsOffset = pSwData->statsOffset;

pSwCtrl->aleOffset = pSwData->aleOffset;

pSwCtrl->mdioOffset = pSwData->mdioOffset;

pSwCtrl->wrOffset = pSwData->wrOffset;

pSwCtrl->cpdmaHdpOffset = pSwData->cpdmaHdpOffset;

pSwCtrl->workMode = pSwData->workMode;

chipVerGetFunc = (FUNCPTR) pSwData->chipVerGetFunc;

DBG_MSG("pSwCtrl->cpswBase = 0x%08x\n", pSwCtrl->cpswBase);

DBG_MSG("pSwCtrl->portOffset = 0x%08x\n", pSwCtrl->portOffset);

DBG_MSG("pSwCtrl->cpdmaOffset = 0x%08x\n", pSwCtrl->cpdmaOffset);

DBG_MSG("pSwCtrl->statsOffset = 0x%08x\n", pSwCtrl->statsOffset);

DBG_MSG("pSwCtrl->aleOffset = 0x%08x\n", pSwCtrl->aleOffset);

DBG_MSG("pSwCtrl->mdioOffset = 0x%08x\n", pSwCtrl->mdioOffset);

DBG_MSG("pSwCtrl->wrOffset = 0x%08x\n", pSwCtrl->wrOffset);

DBG_MSG("pSwCtrl->cpdmaHdpOffset = 0x%08x\n", pSwCtrl->cpdmaHdpOffset);

DBG_MSG("pSwCtrl->workMode = 0x%08x\n", pSwCtrl->workMode);

if (chipVerGetFunc != NULL) {

pSwCtrl->chipVersion = chipVerGetFunc();

}

if (pSwCtrl->workMode != CPSW_MODE_INDEPENDENT_PORT) {

DBG_MSG("workMode is not independent mode\n");

goto failed;

}

/*

* NOTE: there are many resource are shared by multi port,

* cpswDevSem is used to protect these resource

*/

pSwCtrl->cpswDevSem = semMCreate(SEM_Q_PRIORITY |

SEM_DELETE_SAFE |

SEM_INVERSION_SAFE);

if (pSwCtrl->cpswDevSem == NULL) {

DBG_MSG("can not create semaphore cpswDevSem\n");

goto failed;

}

/* initialize host(cpu) port */

if (cpswHostPortInit(pSwCtrl) != OK)

goto failed;

/* initialize DMA module */

if (cpswDmaInit(pSwCtrl) != OK)

goto failed;

return OK;

failed:

if (pSwCtrl->cpswDevSem) {

(void) semDelete(pSwCtrl->cpswDevSem);

}

free(pSwCtrl);

pSwCtrl = NULL;

return ERROR;

}

/*******************************************************************************

*

* cpswHostPortInit - initialize CPSW host port

*

* This routine initializes the CPSW host port. It performs a soft reset, clears &

* enables the ALE module (NOTE: ALE must be enabled otherwise all packets will be

* dropped), and puts port in forward state. MDIO module is enabled in this routine

* (NOTE: if soft reset fails, the routine won't proceed. An error message will be

* print out if debug mode is enabled)

*

* RETURNS: OK or ERROR if reset timeout

*

* ERRNO: N/A

*/

LOCAL STATUS cpswHostPortInit(CPSW_SW_CTRL *pSwCtrl) {

UINT32 base, val;

if (cpswSoftReset(pSwCtrl, CPSW_SOFT_RESET, CPSW_TIMEOUT_VAL) != OK) {

DBG_MSG("host port soft reset failed\n");

return ERROR;

}

DBG_MSG("cpswSoftReset done\n");

base = pSwCtrl->aleOffset;

val = CPSW_ALE_EN_TABLE | CPSW_ALE_CLR_TABLE;

if (pSwCtrl->workMode == CPSW_MODE_INDEPENDENT_PORT)

val |= CPSW_ALE_VLAN_AWARE;

ECSR_WRITE_4(pSwCtrl, base + CPSW_ALE_CONTROL, val);

ECSR_WRITE_4(pSwCtrl, base + CPSW_ALE_PORTCTL(pSwCtrl->hostPortIndex),

CPSW_ALE_PORT_FW | CPSW_ALE_CTL_NO_LEARN);

/* enable statistics for all port */

ECSR_WRITE_4(pSwCtrl, CPSW_STAT_PORT_EN, 7);

base = pSwCtrl->portOffset;

ECSR_WRITE_4(pSwCtrl, base + CPSW_TX_PRI_MAP, CPSW_TX_PRI_MAP_DFTL);

ECSR_WRITE_4(pSwCtrl, base + CPSW_CPDMA_TX_PRI_MAP, CPDMA_TX_PRI_MAP_DFTL);

if (pSwCtrl->workMode == CPSW_MODE_INDEPENDENT_PORT) {

/* set tx fifo into dual emac mode */

val = ECSR_READ_4(pSwCtrl, base + CPSW_TX_IN_CTL);

val = val & ~(CPSW_TX_IN_SEL_MSK << CPSW_TX_IN_SEL_SHIFT);

ECSR_WRITE_4(pSwCtrl, base + CPSW_TX_IN_CTL,

val | (CPSW_TX_FIFO_DUAL_EMAC << CPSW_TX_IN_SEL_SHIFT));

}

base = pSwCtrl->mdioOffset;

ECSR_WRITE_4(pSwCtrl, base + CPSW_MDIO_CONTROL,

CPSW_MDIO_EN | CPSW_MDIO_CLK_DIV);

return OK;

}

/*******************************************************************************

*

* cpswMacPortInit - initialize CPSW GMAC port

*

* This routine initializes the CPSW GMAC port. It performs a soft reset, sets up

* neccessary reigsters, and finally get MAC address from BSP. (NOTE: if soft

* reset fails, the routine won't proceed. An error message will be print out if

* debug mode is enabled)

*

* RETURNS: OK or ERROR if reset timeout

*

* ERRNO: N/A

*/

LOCAL STATUS cpswGmacPortInit(CPSW_DRV_CTRL *pDrvCtrl) {

UINT32 lo, hi;

UINT32 base;

VXB_DEVICE_ID pDev = pDrvCtrl->pDev;

/*

* put MAC port into forward state and disable learning on this port,

* because we are operating in independent port mode, not switch mode.

* We add our MAC address manually.

*/

base = pSwCtrl->aleOffset;

ECSR_WRITE_4(pSwCtrl, base + CPSW_ALE_PORTCTL(pDrvCtrl->portIndex),

CPSW_ALE_PORT_FW | CPSW_ALE_CTL_NO_LEARN);

base = pDrvCtrl->portOffset;

ECSR_WRITE_4(pSwCtrl, base + CPSW_TX_PRI_MAP, CPSW_TX_PRI_MAP_DFTL);

/*

* get our MAC address from BSP. In dual emac mode

* every gmac port has its own MAC address

*/

sysNetMacNVRamAddrGet(pDev->pName, pDev->unitNumber, pDrvCtrl->macaddr,

ETHER_ADDR_LEN);

lo = (pDrvCtrl->macaddr[0] << 8) | pDrvCtrl->macaddr[1];

hi = (pDrvCtrl->macaddr[2] << 24) | (pDrvCtrl->macaddr[3] << 16)

| (pDrvCtrl->macaddr[4] << 8) | pDrvCtrl->macaddr[5];

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->portOffset + CPSW_SL_SA_L0, lo);

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->portOffset + CPSW_SL_SA_HI, hi);

/* reset the gmac module */

base = pDrvCtrl->gmacOffset;

if (cpswSoftReset(pSwCtrl, base + CPSW_SL_MAC_SOFT_RESET,

CPSW_TIMEOUT_VAL) != OK) {

DBG_MSG("%s%d gmac port soft reset timeout\n",

pDev->pName, pDev->unitNumber);

return ERROR;

}

ECSR_WRITE_4(pSwCtrl, base + CPSW_SL_RX_PRI_MAP, CPDMA_TX_PRI_MAP_DFTL);

ECSR_WRITE_4(pSwCtrl, base + CPSW_SL_RX_MAXLEN, CPSW_MTU);

ECSR_WRITE_4(pSwCtrl, base + CPSW_SL_MAC_CTL, CPSW_GMII_EN);

if (pSwCtrl->workMode == CPSW_MODE_INDEPENDENT_PORT) {

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->portOffset + CPSW_PORT_VLAN,

pDrvCtrl->portVlan);

cpswAleAddVlan(pSwCtrl,

(0x1 << pSwCtrl->hostPortIndex) | (0x1 << pDrvCtrl->portIndex),

0, 0, 0, pDrvCtrl->portVlan);

cpswAleAddUniCast(pSwCtrl, pDrvCtrl->macaddr, pDrvCtrl->portVlan, 1, 0,

pSwCtrl->hostPortIndex);

}

return OK;

}

/*******************************************************************************

*

* cpswDmaChanRequest - request a DMA channel

*

* This routine allocates a DMA resource for a given request. The requested

* channel number is specified through the parameter "idx". If "rx" is TRUE, then

* it is asssumed the allocation is for rx channel otherwise it is assumed for

* tx channle. DMA is shared resource, so this routine must be called with

* semaphore taken.

*

* RETURNS: OK or ERROR if allocation fails.

*

* ERRNO: N/A

*/

LOCAL STATUS cpswDmaChanRequest(CPSW_SW_CTRL *pSwCtrl, BOOL rx, int chanNum) {

UINT8 *pChanArray;

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

if (rx == TRUE)

pChanArray = pSwCtrl->cpswRxDmaChans;

else

pChanArray = pSwCtrl->cpswTxDmaChans;

if (0 <= chanNum && chanNum < NR_DMA_CHANS) {

if (!pChanArray[chanNum]) {

pChanArray[chanNum] = 1;

(void) semGive(pSwCtrl->cpswDevSem);

return OK;

}

}

(void) semGive(pSwCtrl->cpswDevSem);

return ERROR;

}

/*******************************************************************************

*

* cpswDmaChanRelease - release a DMA channel

*

* This routine releases a DMA resource for a given request. The requested

* channel number is specified through the parameter "idx". If "rx" is TRUE, then

* it is asssumed the release operation is for rx channel otherwise it is assumed

* for tx channle. If a already-free channel is given for release, this routine

* also returns OK. DMA is shared resource, so this routine must be called with

* semaphore taken.

*

* RETURNS: OK or ERROR if release operation fails.

*

* ERRNO: N/A

*/

LOCAL STATUS cpswDmaChanRelease(CPSW_SW_CTRL *pSwCtrl, BOOL rx, int chanNum) {

UINT8 *pChanArray;

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

if (rx == TRUE)

pChanArray = pSwCtrl->cpswRxDmaChans;

else

pChanArray = pSwCtrl->cpswTxDmaChans;

if (0 <= chanNum && chanNum < NR_DMA_CHANS) {

if (!pChanArray[chanNum]) {

(void) semGive(pSwCtrl->cpswDevSem);

return OK;

} else {

pChanArray[chanNum] = 0;

(void) semGive(pSwCtrl->cpswDevSem);

return OK;

}

}

(void) semGive(pSwCtrl->cpswDevSem);

return ERROR;

}

/*******************************************************************************

*

* cpswDmaInit - initialize CPDMA module

*

* This routine initializes the CPDMA module inside the NIC. This routine will

* perform a soft reset, clear all the rx/tx header decriptor pointer/completion

* header pointer, disable interrupts and set the CPDMA control register to

* default value:

*

* frames containing overrun error are filtered

* DMA writes offset/len field in the descritpor

* DMA clears the owership bit

* All 8 DMA queue uses the round-robin scheduling algorithm

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL STATUS cpswDmaInit(CPSW_SW_CTRL *pSwCtrl) {

int i;

#ifdef CPSW_DBG

UINT32 val;

#endif /* CPSW_DBG */

/* reset the dma module */

if (cpswSoftReset(pSwCtrl, pSwCtrl->cpdmaOffset + CPDMA_SOFT_RESET,

CPSW_TIMEOUT_VAL) != OK) {

DBG_MSG("cpdma module soft reset timeout\n");

return ERROR;

}

/* initialize dma queue header pointers */

for (i = 0; i < NR_DMA_CHANS; i++) {

CPDMA_REG_WRITE(pSwCtrl, CPDMA_TX_HDP(i), 0);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_HDP(i), 0);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_TX_CP(i), 0);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_CP(i), 0);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_FREEBUF(i), 0);

}

CPDMA_REG_WRITE(pSwCtrl, CPDMA_DMACONTROL, CPDMA_CONTROL_DEFAULT);

/* disable channel interrupts */

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_BUFOFFSET, 0x0);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_TX_INTMASK_CLR, 0xffff);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_RX_INTMASK_CLR, 0xffff);

CPDMA_REG_WRITE(pSwCtrl, CPDMA_INTMASK_CLR, 0x3);

#ifdef CPSW_DBG

val = CPDMA_REG_READ(pSwCtrl, CPDMA_RX_INTSTAT_MASKED);

if (val & 0xffff)

{

DBG_MSG("rx mask(0x%08x) is not zero\n", val);

}

val = CPDMA_REG_READ(pSwCtrl, CPDMA_TX_INTSTAT_MASKED);

if (val & 0xffff)

{

DBG_MSG("tx mask(0x%08x) is not zero\n", val);

}

#endif /* CPSW_DBG */

/* enable global tx rx DMA */

CPDMA_TX_EN(pSwCtrl);

CPDMA_RX_EN(pSwCtrl);

return OK;

}

/*******************************************************************************

*

* cpswSoftReset - perform soft reset on a given module

*

* This routine performs soft reset on a given module.

*

* RETURNS: OK or ERROR if timeout

*

* ERRNO: N/A

*/

LOCAL STATUS cpswSoftReset(CPSW_SW_CTRL *pSwCtrl, UINT32 moduleReg,

UINT32 timeout) {

UINT32 i = 0;

UINT32 ret;

ECSR_WRITE_4(pSwCtrl, moduleReg, 0x1);

do {

ret = ECSR_READ_4(pSwCtrl, moduleReg);

} while ((ret & 0x1) && (i++ < timeout));

if (i >= timeout)

return ERROR;

return OK;

}

/*******************************************************************************

*

* cpswInstUnlink - unlink the device instance from VxBus subsystem

*

* This routine unlinks the device instance from VxBus subsystem

*

* RETURNS: OK or ERROR if operation failed.

*

* ERRNO: N/A

*/

LOCAL STATUS cpswInstUnlink(VXB_DEVICE_ID pDev, void *unused) {

CPSW_DRV_CTRL *pDrvCtrl = pDev->pDrvCtrl;

if (pDrvCtrl->cookie != NULL) {

if (muxDevStop(pDrvCtrl->cookie) != OK) {

DBG_MSG("%s%d muxDevStop return ERROR\n",

pDev->pName, pDev->unitNumber);

return ERROR;

}

if (muxDevUnload(pDev->pName, pDev->unitNumber) != OK) {

DBG_MSG("%s%d muxDevUnload return ERROR\n",

pDev->pName, pDev->unitNumber);

return ERROR;

}

}

/* free the memory of ring descriptor */

if (pDrvCtrl->cpswTxDescMem)

cacheDmaFree(pDrvCtrl->cpswTxDescMem);

if (pDrvCtrl->cpswRxDescMem)

cacheDmaFree(pDrvCtrl->cpswRxDescMem);

/* destroy our MII bus and child PHYs */

if (pDrvCtrl->cpswMiiBus != NULL) {

miiBusDelete(pDrvCtrl->cpswMiiBus);

}

/* disconnect the ISR handle */

(void) vxbIntDisconnect(pDev, 0, cpswEndTxInt, pSwCtrl);

(void) vxbIntDisconnect(pDev, 1, cpswEndRxInt, pSwCtrl);

(void) vxbIntDisconnect(pDev, 2, cpswEndMiscInt, pSwCtrl);

/* destroy the adapter context */

free(pDrvCtrl);

pDev->pDrvCtrl = NULL;

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

pSwCtrl->refCount--;

pSwCtrl->port[pDev->unitNumber] = NULL;

(void) semGive(pSwCtrl->cpswDevSem);

if (pSwCtrl->refCount == 0) {

/* disable global tx rx DMA */

CPDMA_TX_DIS(pSwCtrl);

CPDMA_RX_DIS(pSwCtrl);

(void) semDelete(pSwCtrl->cpswDevSem);

free(pSwCtrl);

pSwCtrl = NULL;

DBG_MSG("%s%d: pSwCtrl is freed for all the port are freed\n",

pDev->pName, pDev->unitNumber);

}

return OK;

}

/*******************************************************************************

*

* cpswAleRead - read an ALE entry

*

* This routine reads an ALE entry from the given index

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL void cpswAleRead(CPSW_SW_CTRL *pSwCtrl, CPSW_ALE_TBL *tbl, UINT32 entry) {

ECSR_WRITE_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_TBLCTL,

entry & CPSW_ALE_ENTRY_IDX_MASK);

tbl->word0 = ECSR_READ_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_WORD0);

tbl->word1 = ECSR_READ_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_WORD1);

tbl->word2 = ECSR_READ_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_WORD2) & 0xf;

}

/*******************************************************************************

*

* cpswAleWrite - write an ALE entry

*

* This routine writes data to an ALE entry with the given index

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

LOCAL void cpswAleWrite(CPSW_SW_CTRL *pSwCtrl, CPSW_ALE_TBL *tbl, UINT32 entry) {

ECSR_WRITE_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_WORD0, tbl->word0);

ECSR_WRITE_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_WORD1, tbl->word1);

ECSR_WRITE_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_WORD2, tbl->word2 & 0xf);

ECSR_WRITE_4(pSwCtrl, pSwCtrl->aleOffset + CPSW_ALE_TBLCTL,

(entry & CPSW_ALE_ENTRY_IDX_MASK) | CPSW_ALE_WRITE);

}

/*******************************************************************************

*

* cpswAleFind - find an emtpy ALE entry

*

* This routine finds an emtpy ALE entry.

*

* RETURNS: empty entry index or -1 if ALE is full

*

* ERRNO: N/A

*/

LOCAL int cpswAleFind(CPSW_SW_CTRL *pSwCtrl) {

int i;

CPSW_ALE_TBL tbl;

for (i = 0; i < CPSW_ALE_ENTRY_NR; i++) {

cpswAleRead(pSwCtrl, &tbl, i);

if ((tbl.word1 & CPSW_ALE_ENTRY_MASK) == 0x0)

return i;

}

return -1;

}

/*******************************************************************************

*

* cpswAleMatch - find the entry with the given MAC address

*

* This routine finds the entry with the given MAC address

*

* RETURNS: entry found or -1 if the MAC address has not entered into ALE yet.

*

* ERRNO: N/A

*/

LOCAL int cpswAleMatch(CPSW_SW_CTRL *pSwCtrl, unsigned char *mac) {

int i;

CPSW_ALE_TBL t;

unsigned int word0, word1;

word0 = (mac[2] << 24) | (mac[3] << 16) | (mac[4] << 8) | (mac[5]);

word1 = (mac[0] << 8) | (mac[1]);

for (i = 0; i < CPSW_ALE_ENTRY_NR; i++) {

cpswAleRead(pSwCtrl, &t, i);

if ((t.word0 == word0) && ((t.word1 & 0xffff) == word1))

return i;

}

return -1;

}

/*******************************************************************************

*

* cpswAleEntryShow - show an ALE entry

*

* This routine outputs verbose message of an ALE entry

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

void cpswAleEntryShow(CPSW_ALE_TBL *tbl) {

unsigned char *macaddr;

unsigned char *macaddr1;

int block = 0, secure = 0, port = 0, portmask = 0;

int fwstate = 0, super = 0;

int unicasttype = 0;

int vmem = 0, umf = 0, rmf = 0, fue = 0;

char *str = NULL;

static char *unicast[] = { "u/na", "u/a/nt", "oui", "u/a/t" };

macaddr = (unsigned char *) &tbl->word0;

macaddr1 = (unsigned char *) &tbl->word1;

int vid = (tbl->word1 >> 16) & 0xfff;

int type = (tbl->word1 >> 28) & 0x3;

int multicast = tbl->word1 & 0x100;

if (type == 0x0)

return;

if (type == 1) {

if (multicast)

str = "multicast";

else

str = "unicast";

} else if (type == 0x3) {

if (multicast)

str = "multi/vlan";

else

str = "uni/vlan";

}

if (type == 0x2) {

str = "vlan";

fue = (tbl->word0 >> 24) & 0x7;

rmf = (tbl->word0 >> 16) & 0x7;

umf = (tbl->word0 >> 8) & 0x7;

vmem = tbl->word0 & 0x7;

} else {

if (!multicast) {

unicasttype = (tbl->word1 >> 30) & 0x3;

secure = (tbl->word2 & 0x1);

block = (tbl->word2 & 0x2) >> 1;

port = (tbl->word2 >> 0x2) & 0x3;

} else {

fwstate = (tbl->word1 >> 30) & 0x3;

super = (tbl->word2 >> 1) & 0x1;

portmask = (tbl->word2 >> 2) & 0x7;

}

}

if (type == 0x3 || type == 0x1) {

/* multicast entry */

if (multicast) {

printf("%-20s%-20s%-20s%-20s%-20s%-20s\n", "mac", "ent type",

"state", "super", "portmask", "vid");

printf("---------------------------------------------"

"---------------------------------------------"

"-----------------------------------\n");

printf("%02x:%02x:%02x:%02x:%02x:%02x %-20s%"

"-20d%-20d%-20d%-20d\n\n", macaddr1[1], macaddr1[0],

macaddr[3], macaddr[2], macaddr[1], macaddr[0], str,

fwstate, super, portmask, vid);

}

/* unicast entry */

else {

printf("%-20s%-20s%-20s%-20s%-20s%-20s%-20s\n", "mac", "ent type",

"type", "secure", "block", "port", "vid");

printf("---------------------------------------------"

"---------------------------------------------"

"-----------------------------------\n");

printf("%02x:%02x:%02x:%02x:%02x:%02x %-20s%"

"-20s%-20d%-20d%-20d%-20d\n\n", macaddr1[1], macaddr1[0],

macaddr[3], macaddr[2], macaddr[1], macaddr[0], str,

unicast[unicasttype], secure, block, port, vid);

}

/* vlan entry */

/* } else if (type == 0x2) {*/

} else {

printf("%-20s%-20s%-20s%-20s%-20s%-20s%-20s\n", "mac", "ent type",

"fue", "rmf", "umf", "vmem", "vid");

printf("---------------------------------------------"

"---------------------------------------------"

"-----------------------------------\n");

printf("%-20s%-20s%-20d%-20d%-20d%-20d%-20d\n\n", "N/A", str, fue, rmf,

umf, vmem, vid);

}

}

/*******************************************************************************

*

* cpswAleDump - show all the ALE entries

*

* This routine outputs verbose message of all the ALE entries

*

* RETURNS: N/A

*

* ERRNO: N/A

*/

void cpswAleDump(void) {

int i;

CPSW_ALE_TBL tbl;

for (i = 0; i < CPSW_ALE_ENTRY_NR; i++) {

cpswAleRead(pSwCtrl, &tbl, i);

cpswAleEntryShow(&tbl);

}

}

/*******************************************************************************

*

* cpswAleAddMultiCast - add a multicast MAC address into ALE table

*

* This routine adds a multicast MAC address into ALE table. First, this routine

* will try to find a match. If the MAC address is already in the table, it

* overwrites the entry content with new values. If it can not find a match, a empty

* entry will be allocated and the MAC address will be added.

*

* RETURNS: 0 on success, ENOMEM if can not find a emtpy entry

*

* ERRNO: N/A

*/

LOCAL int cpswAleAddMultiCast(CPSW_SW_CTRL *pSwCtrl, unsigned char *mac,

int vid, int fwstate, int super, int portmask) {

unsigned int word0, word1;

CPSW_ALE_TBL tbl;

int entry;

word0 = (mac[2] << 24) | (mac[3] << 16) | (mac[4] << 8) | (mac[5]);

word1 = (mac[0] << 8) | (mac[1]);

entry = cpswAleMatch(pSwCtrl, mac);

if (entry < 0) {

entry = cpswAleFind(pSwCtrl);

if (entry < 0)

return ENOMEM;

}

tbl.word0 = word0;

/* multicast with vlan */

if (vid > 0)

tbl.word1 = word1 | ((vid & 0xfff) << 16) | ((fwstate & 0x3) << 30)

| (0x3 << 28);

else

tbl.word1 = word1 | ((fwstate & 0x3) << 30) | (0x1 << 28);

tbl.word2 = ((super & 0x1) << 1) | ((portmask & 0x7) << 2);

cpswAleWrite(pSwCtrl, &tbl, entry);

return 0;

}

/*******************************************************************************

*

* cpswAleAddUniCast - add a unicast MAC address into ALE table

*

* This routine adds a unicast MAC address into ALE table. First, this routine

* will try to find a match. If the MAC address is already in the table, it overwrites

* that entry content with new values. If it can not find a match,

* a empty entry will be allocated and the MAC address will be added.

*

* RETURNS: 0 on success or ENOMEM if can not find a emtpy entry

*

* ERRNO: N/A

*/

LOCAL int cpswAleAddUniCast(CPSW_SW_CTRL *pSwCtrl, unsigned char *mac, int vid,

int secure, int block, int port) {

unsigned int word0, word1;

CPSW_ALE_TBL tbl;

int entry;

word0 = (mac[2] << 24) | (mac[3] << 16) | (mac[4] << 8) | (mac[5]);

word1 = (mac[0] << 8) | (mac[1]);

tbl.word0 = word0;

tbl.word1 = word1;

tbl.word2 = 0x0;

entry = cpswAleMatch(pSwCtrl, mac);

if (entry < 0) {

entry = cpswAleFind(pSwCtrl);

if (entry < 0)

return ENOMEM;

}

tbl.word0 = word0;

/* unicast with vlan*/

if (vid > 0)

tbl.word1 = word1 | (0x3 << 28) |

CPSW_ALE_UNICAST_AGEABLE_NOT | ((vid & 0xfff) << 16);

else

tbl.word1 = word1 | (0x1 << 28) |

CPSW_ALE_UNICAST_AGEABLE_NOT;

tbl.word2 = ((block & 0x1) << 1) | (secure & 0x1) | ((port & 0x3) << 2);

cpswAleWrite(pSwCtrl, &tbl, entry);

return 0;

}

/*******************************************************************************

*

* cpswAleMatchVlan - find the ALE entry with the given vid

*

* This routine finds the ALE entry index with the given vid

*

* RETURNS: ALE entry index on success or -1 if entry not found

*

* ERRNO: N/A

*/

LOCAL int cpswAleMatchVlan(CPSW_SW_CTRL *pSwCtrl, int vid) {

int i;

CPSW_ALE_TBL t;

for (i = 0; i < CPSW_ALE_ENTRY_NR; i++) {

cpswAleRead(pSwCtrl, &t, i);

if (((t.word1 >> 28) & 0x3) == 0x2) {

if (((t.word1 >> 16) & 0xfff) == vid)

return i;

}

}

return -1;

}

/*******************************************************************************

*

* cpswAleAddVlan - add a vlan entry into ALE table

*

* This routine adds a vlan entry into ALE table

*

* RETURNS: 0 on success, ENOMEM if can not find a emtpy entry or

* EEXIST if the given vlan is alreay in ALE table

*

* ERRNO: N/A

*/

LOCAL int cpswAleAddVlan(CPSW_SW_CTRL *pSwCtrl, int vlanMemberList,

int unregFloodMask, int regFloodMask, int forceUntaggedEgress, int vid) {

CPSW_ALE_TBL t;

int entry;

if (vid <= 0 || vid >= 4095)

return EINVAL;

entry = cpswAleMatchVlan(pSwCtrl, vid);

if (entry < 0) {

entry = cpswAleFind(pSwCtrl);

if (entry < 0)

return ENOMEM;

}

t.word0 = ((vlanMemberList & 0x7)) | ((unregFloodMask & 0x7) << 8)

| ((regFloodMask & 0x7) << 16)

| ((forceUntaggedEgress & 0x7) << 24);

t.word1 = ((vid & 0xfff) << 16) | (0x2 << 28);

t.word2 = 0;

cpswAleWrite(pSwCtrl, &t, entry);

return 0;

}

/*******************************************************************************

*

* cpswPhyRead - miiBus miiRead method

*

* This function implements an miiRead() method that allows PHYs

* on the miiBus to access our MII management registers.

*

* RETURNS: ERROR if invalid PHY addr, else OK

*

* ERRNO: N/A

*/

STATUS cpswPhyRead(VXB_DEVICE_ID pDev, UINT8 phyAddr, UINT8 regAddr,

UINT16 *pDataVal) {

UINT32 ret;

UINT32 index = 0;

CPSW_DRV_CTRL *pDrvCtrl = pDev->pDrvCtrl;

if (phyAddr >= 32)

return ERROR;

/* we only work on the exactly phy address which is specified */

if (pDrvCtrl->cpswPhyAddr != phyAddr) {

*pDataVal = 0xFFFF;

return ERROR;

}

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

do {

ret = ECSR_READ_4(pSwCtrl,

pSwCtrl->mdioOffset + CPSW_USERACCESSn(index));

} while (ret & CPSW_MDIO_GO);

ret = phyAddr << CPSW_PHY_ADDR_SHIFT | regAddr << CPSW_REG_ADDR_SHIFT |

CPSW_MDIO_GO;

ECSR_WRITE_4(pSwCtrl, pSwCtrl->mdioOffset + CPSW_USERACCESSn(index), ret);

do {

ret = ECSR_READ_4(pSwCtrl,

pSwCtrl->mdioOffset + CPSW_USERACCESSn(index));

} while (ret & CPSW_MDIO_GO);

*pDataVal = ret & 0xffff;

(void) semGive(pSwCtrl->cpswDevSem);

return OK;

}

/*******************************************************************************

*

* cpswPhyWrite - miiBus miiWrite method

*

* This function implements an miiWrite() method that allows PHYs

* on the miiBus to access our MII management registers. This routine

* works in much the same way as cpswPhyRead(), using the shortcut

* PHY management registers to make it look like there's a single

* PHY at MII address 0.

*

* RETURNS: ERROR if invalid PHY addr, else OK

*

* ERRNO: N/A

*/

STATUS cpswPhyWrite(VXB_DEVICE_ID pDev, UINT8 phyAddr, UINT8 regAddr,

UINT16 dataVal) {

UINT32 ret;

UINT32 index = 0;

CPSW_DRV_CTRL *pDrvCtrl = pDev->pDrvCtrl;

if (phyAddr >= 32)

return ERROR;

/* we only work on the exactly phy address which is specified */

if (pDrvCtrl->cpswPhyAddr != phyAddr)

return ERROR;

(void) semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

do {

ret = ECSR_READ_4(pSwCtrl,

pSwCtrl->mdioOffset + CPSW_USERACCESSn(index));

} while (ret & CPSW_MDIO_GO);

ret = phyAddr << CPSW_PHY_ADDR_SHIFT | regAddr << CPSW_REG_ADDR_SHIFT |

CPSW_MDIO_GO | CPSW_MDIO_WRITE | dataVal;

ECSR_WRITE_4(pSwCtrl, pSwCtrl->mdioOffset + CPSW_USERACCESSn(index), ret);

do {

ret = ECSR_READ_4(pSwCtrl,

pSwCtrl->mdioOffset + CPSW_USERACCESSn(index));

} while (ret & CPSW_MDIO_GO);

(void) semGive(pSwCtrl->cpswDevSem);

return OK;

}

/*****************************************************************************

*

* cpswLinkUpdate - miiBus miiLinkUpdate method

*

* This function implements an miiLinkUpdate() method that allows

* miiBus to notify us of link state changes. This routine will be

* invoked by the miiMonitor task when it detects a change in link

* status. Normally, the miiMonitor task checks for link events every

* two seconds.

*

* Once we determine the new link state, we will announce the change

* to any bound protocols via muxError(). We also update the ifSpeed

* fields in the MIB2 structures so that SNMP queries can detect the

* correct link speed.

*

* RETURNS: ERROR if obtaining the new media setting fails, else OK

*

* ERRNO: N/A

*/

LOCAL STATUS cpswLinkUpdate(VXB_DEVICE_ID pDev) {

CPSW_DRV_CTRL *pDrvCtrl;

UINT32 oldStatus;

UINT32 val;

if (pDev->pDrvCtrl == NULL)

return ERROR;

pDrvCtrl = pDev->pDrvCtrl;

if (pDrvCtrl->cpswMiiBus == NULL)

return ERROR;

semTake(pSwCtrl->cpswDevSem, WAIT_FOREVER);

oldStatus = pDrvCtrl->cpswCurStatus;

if (miiBusModeGet(pDrvCtrl->cpswMiiBus, &pDrvCtrl->cpswCurMedia,

&pDrvCtrl->cpswCurStatus) == ERROR) {

semGive(pSwCtrl->cpswDevSem);

return ERROR;

}

if (!(pDrvCtrl->cpswEndObj.flags & IFF_UP)) {

semGive(pSwCtrl->cpswDevSem);

return OK;

}

val = ECSR_READ_4(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_CTL);

switch (IFM_SUBTYPE(pDrvCtrl->cpswCurMedia)) {

case (IFM_1000_T):

case (IFM_1000_SX):

val &= ~CPSW_EXT_EN;

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_CTL,

GAMC_CTL_GIG | val);

pDrvCtrl->cpswEndObj.mib2Tbl.ifSpeed = 1000000000;

if (pDrvCtrl->cpswEndObj.pMib2Tbl != NULL) {

pDrvCtrl->cpswEndObj.pMib2Tbl->m2Data.mibIfTbl.ifSpeed = 1000000000;

}

break;

case (IFM_100_TX):

val &= ~CPSW_EXT_EN;

val |= CPSW_RMII_EN_100;

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_CTL,

val & ~GAMC_CTL_GIG);

pDrvCtrl->cpswEndObj.mib2Tbl.ifSpeed = 100000000;

if (pDrvCtrl->cpswEndObj.pMib2Tbl != NULL) {

pDrvCtrl->cpswEndObj.pMib2Tbl->m2Data.mibIfTbl.ifSpeed = 100000000;

}

break;

case (IFM_10_T):

val |= CPSW_EXT_EN;

val &= ~CPSW_RMII_EN_100;

ECSR_WRITE_4(pSwCtrl, pDrvCtrl->gmacOffset + CPSW_SL_MAC_CTL,

val & ~GAMC_CTL_GIG);