Part Number: AM62L

Other Parts Discussed in Thread: DP83867IR,

Tool/software:

Our board has two phy DP83867IR mounted on the MDIO interface.

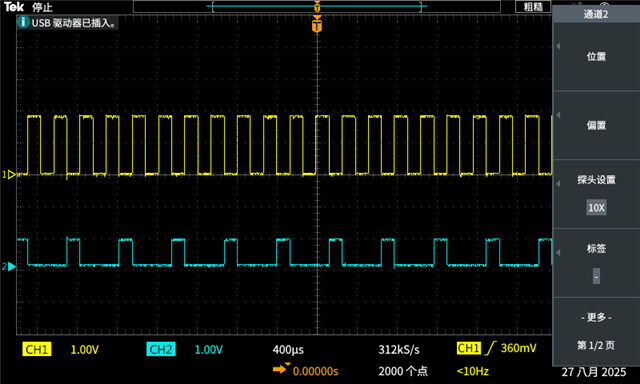

At present, during the cold start test of the board, there is a situation where the mdio bus registration fails, as shown in the figure below. When the problem occurs, the clocks of MDIO and MDC are always in the following state, indicating that the MDIO level is obviously incorrect:

It will print the following kernel log when the issue occur.

[ 1.341594] davinci_mdio 8000f00.mdio: davinci mdio revision 17.7, bus freq 1000000

[ 1.445718] davinci_mdio 8000f00.mdio: timed out waiting for user access

[ 1.552758] davinci_mdio 8000f00.mdio: timed out waiting for idle

[ 1.558865] davinci_mdio 8000f00.mdio: probe with driver davinci_mdio failed with error -5