Other Parts Discussed in Thread: AM62P

Tool/software:

Hi Expert,

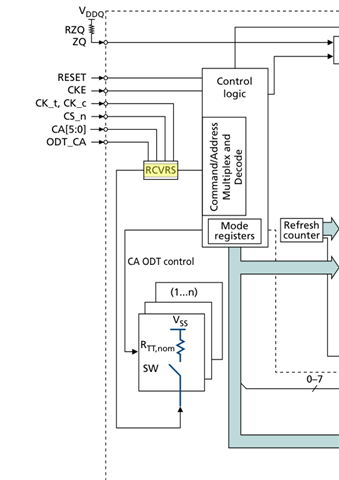

From below guide, I can see the resistor value for others, but there is missing the value of ODT_CA_A/B, do we have any recommend value? In EVM, we are using 10K, but I want to double check about this, is it the best value? because from the Sitara AM62P board, we use 2.2K, and some customer is using 1K, so I want to figure it out, what is the best value? can you share some standard (Memory datasheet or JEDC?) customer need to follow, or any pull up resistor value can be accepted?

Jacinto 7 LPDDR4 Board Design and Layout Guidelines (Rev. F)

BR,

Biao