Tool/software:

Hi,

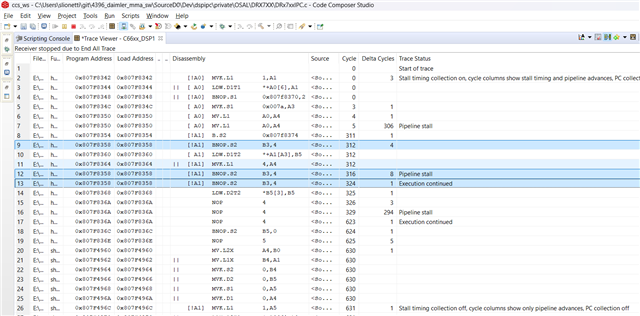

on C66, CCS 10, I'm tracing a simple function that do some checks and when these checks are positive invoke a function derived from an address parameter, I see the instruction

BNOP.S2 B3,4

Taking 4 cycles (row 9, column Delta cycles) as expected

but then the same address is showed again with 8+1 delta cycles.

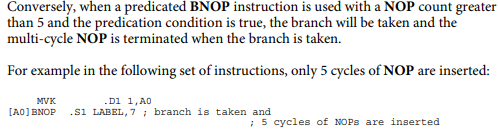

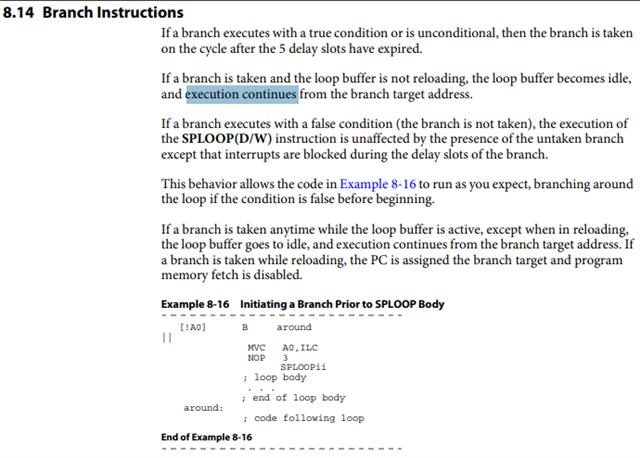

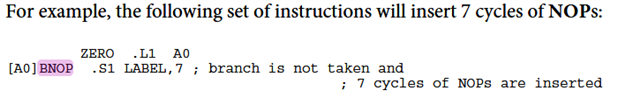

This is not expected, as reported on sprugh7:

Why are these extra cycles reported? Are just a tool artifact?

The trace option is "Custom Core Trace", with Trigger1 "Start trace" at "Point", Trigger2 "Stop trace" at Point.

Thanks for the attention