Other Parts Discussed in Thread: UNIFLASH

Tool/software:

Hello TI Team,

Processor: AM6442

SDK Version: AM64x MCU+ SDK 10.00.00

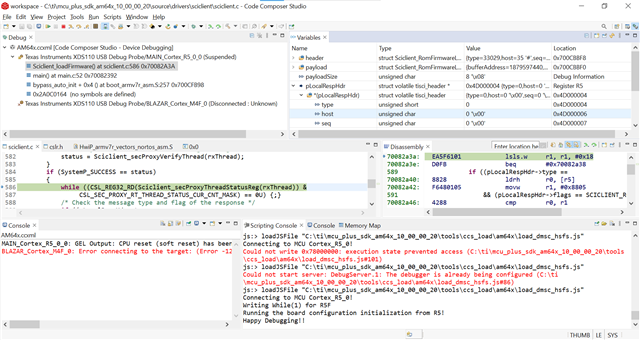

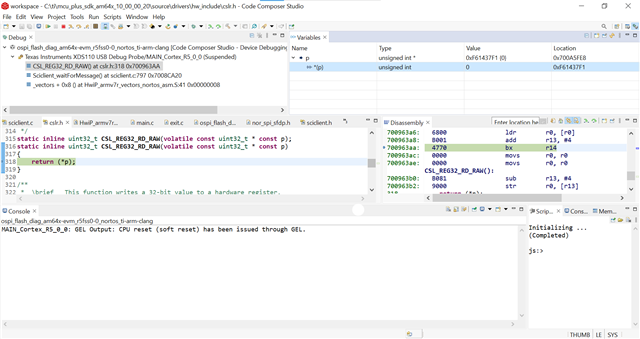

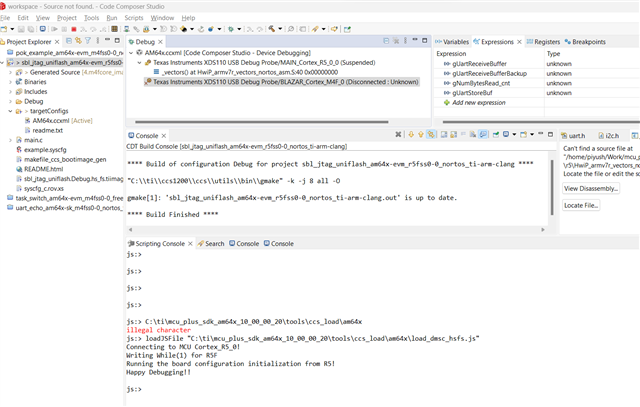

I am currently working with the AM6442 processor using the EVM board to validate the Cortex-M4F core. We have successfully followed the flashing and debugging procedures as outlined in the official guide, and the results are as expected.

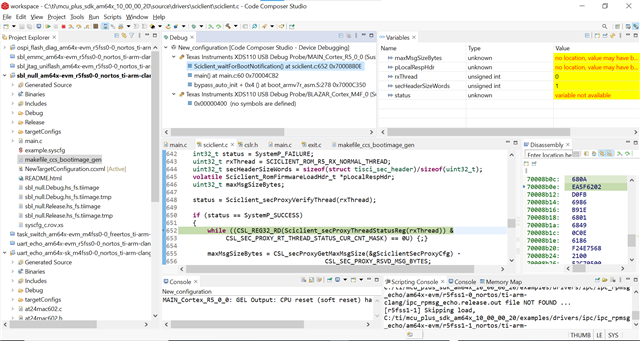

Following this validation, we have moved forward with the development of a custom board. The only changes made compared to the EVM are in the EMMC and OSPI sections due to component availability; the rest of the design around the processor remains unchanged.

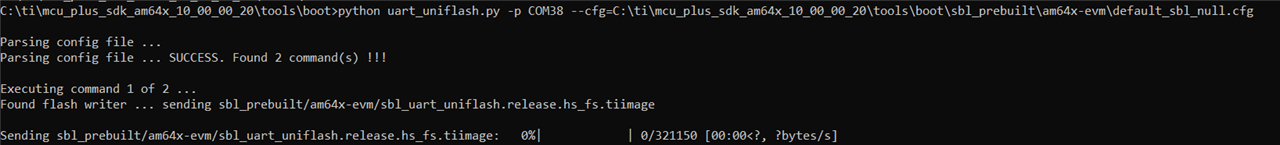

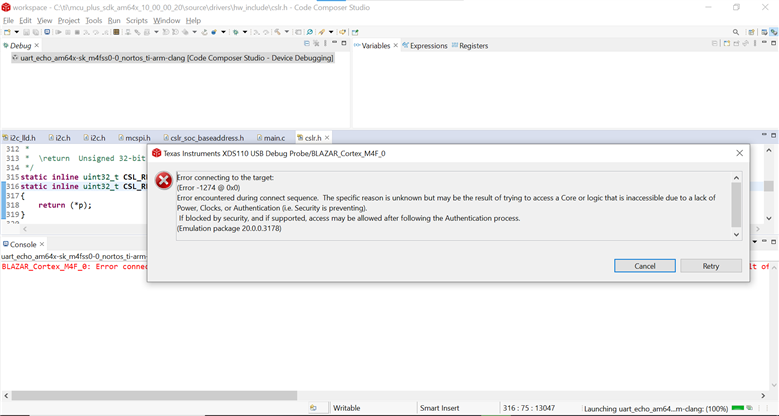

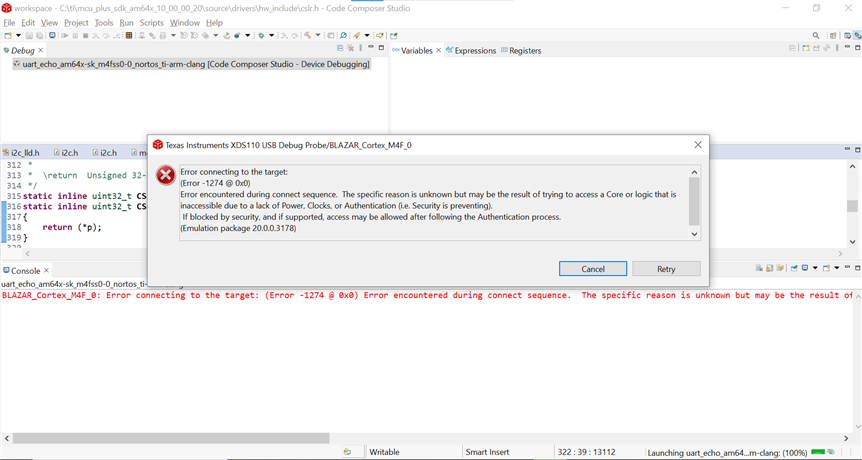

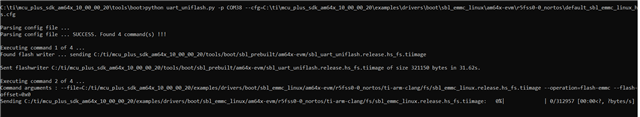

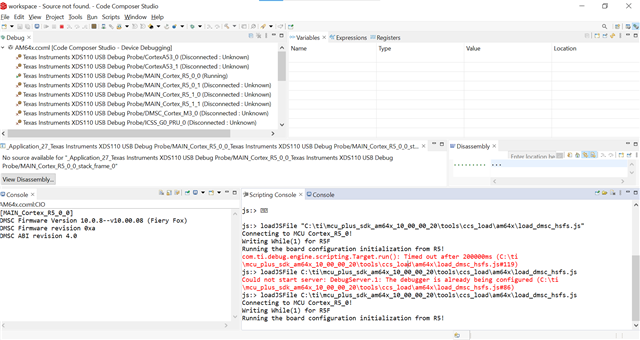

However, on the custom board, we are encountering an issue during the UART Uniflash flashing process using the SBL_prebuilt binary. The process fails at the initial step and does not proceed further.

Query:

a) Unable to flash "default_sbl_null.cfg" boot image?

Requesting your support on this. Please do revert with your inputs.

Thanks and regards,

Ganesh Pawar

:

: