Tool/software:

Hi Expert,

customer have below question, pls help check:

We are currently using the 1588 timestamp function of am6442's cssg1 network port. The related drivers of Icssg are ported from uboot in Linux SDK 9.0, and the IEP driver is ported from Linux code.

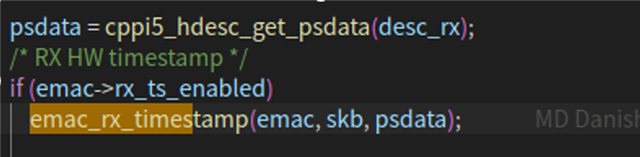

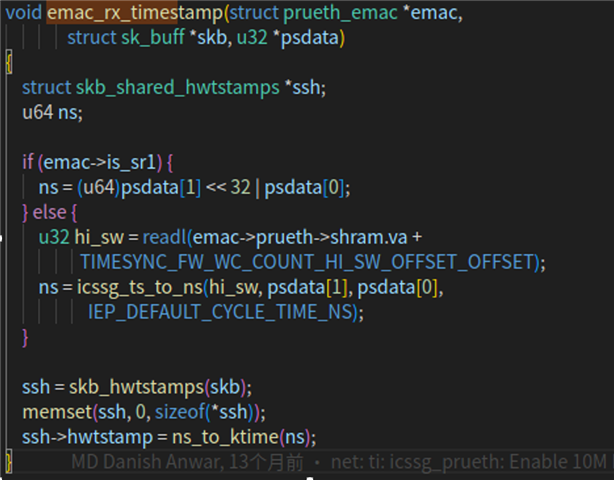

Our current operating system refers to the above code in the Linux driver, and normal timestamps can be obtained from network received messages.

The current network data transmission process of our operating system is : send data ->DMA transmission completion interrupt ->return the transmission completion timestamp. Therefore, it is required that the message sent can obtain the timestamp by reading the DMA descriptor or other external modules during the transmission completion interrupt. We have learned that cadence GMAC IP cores can read timestamps from dam descriptors.

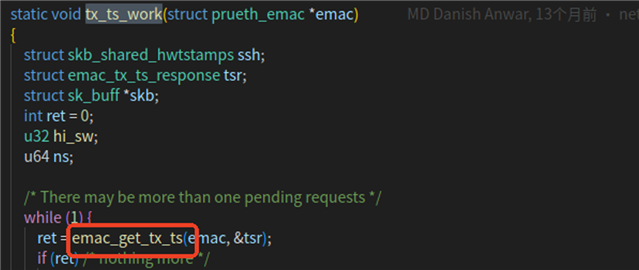

We found that the current Linux driver uses tx_ts0 interrupt to trigger tx_ts_work to read the sending timestamp, which is incompatible with our current mechanism

Can you provide a modification method or example code similar to Cadence's GMAC that obtains the sending timestamp by sending DMA descriptors. The accuracy can be appropriately relaxed.

BR,

Biao