Tool/software:

Hello,

I am trying to flash mine AUTOSAR build application to MCU2_1 with jacinto v7.2.0.6 PSDK.

After launching launch.js for J721E I get following error:

MCU_Cortex_R5_0: Trouble Reading Memory Block at 0x18e59ff0 on Page 0 of Length 0x4: (Error -1205 @ 0x18E59FF0) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178) MCU_Cortex_R5_0: Trouble Reading Memory Block at 0x410163a4 on Page 0 of Length 0x4: (Error -1205 @ 0x410163A4) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178) MCU_Cortex_R5_0: Trouble Reading Memory Block at 0x41c1c214 on Page 0 of Length 0x4: (Error -1205 @ 0x41C1C214) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178)

And since R5_0 core is hitting main then I try to program my binary to MAIN_Cortex_R5_0_1 and then get additional error:

MAIN_Cortex_R5_0_1: Trouble Reading Memory Block at 0x9719e00c on Page 0 of Length 0x4: (Error -1205 @ 0x9719E00C) Device memory bus has an error and may be hung. Verify that the memory address is in valid memory. If error persists, confirm configuration, power-cycle board, and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 20.0.0.3178) MAIN_Cortex_R5_0_1: File Loader: Verification failed: Target failed to read 0x9719E00C MAIN_Cortex_R5_0_1: GEL: File: (...)\StartApplication\Appl\StartApplication.out: Load failed.

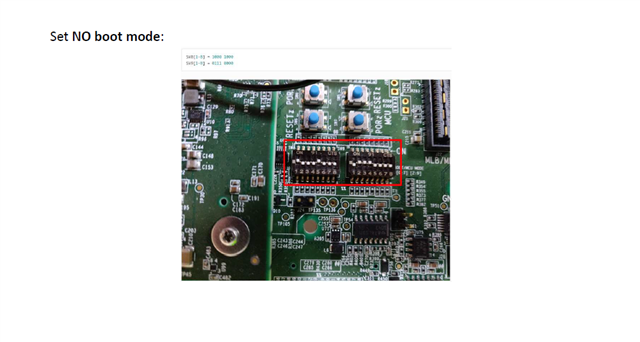

Can you support me to debug the problem? Boot config pins are setup to NO Boot:

Thank you and Best Regards,

Tomislav