Tool/software:

I understand there are 12 PRU cores in total. (2 subsystems, 2 slices per subsystem, 3 cores per slice)

I understand each of the cores has slightly different functionality (PRU / RTU_PRU / TX_PRU).

I understand only the 4x PRU cores have access to the EGPO functionality (not RTU/TX PRU, which can only do EGPI)

I have an application that will be using 3x of the PRU cores for EGPO (shift-out) functionality.

This leaves 1x PRU core, 4x RTU cores and 4x TX cores.

This application also needs to handle deterministic industrial networking (EtherCAT, Profinet IRT, etc).

I am aware of Arcontis EC-Master stack, but I am not familiar with how it works (how many cores, which cores, etc)

Is it possible to implement say the EC-Master using the remaining 1x PRU core?

Can the RTU/TX cores R/W the ethernet rgmii pins?

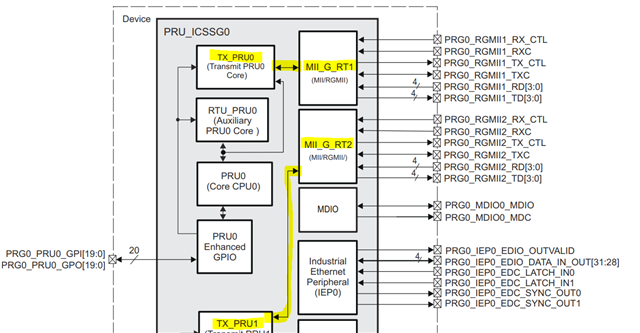

I am looking at Figure 6-177. PRU_ICSSG0 External Interface I/Os from the TRM.

It seems to me that only the TX_PRUx cores can directly control the MII_G_RT ICSSG peripherals?