Other Parts Discussed in Thread: TPS65224

Tool/software:

Hello, engineers

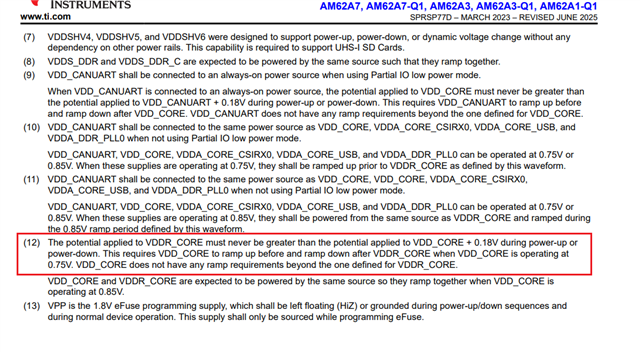

When I was testing the power-down sequence of AM62A7, I found that the manual has such a requirement: VDDR_CORE (0V85) needs to be always less than VDD_CORE (0V75) + 0.18V during the power-down process. That is, during the power-down process, I need to ensure that VDDR_CORE is powered off first before powering off VDD_CORE. Or, during the entire power-down process, the power-off rate of VDDR_CORE should be faster than that of VDD_CORE. Without additional discharge circuits, this is very difficult because the power-down time of the power supply is strongly related to the capacitance value of the attached capacitor.

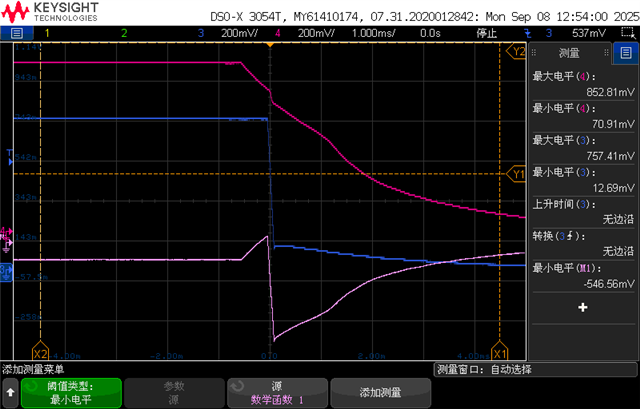

The following waveform is the actual measurement of the power-down timing sequence I conducted using the PMIC TPS65224. The red line represents VDDR_CORE, the blue line represents VDD_CORE, and the purple line represents the difference between VDD_CORE and VDDR_CORE. This subtraction value needs to always be greater than -0.18V. From the test waveform, it can be seen that this clearly does not meet the requirement; however, it can be confirmed that the power-down timing sequence can satisfy that the enable of VDDR_CORE is pulled down first, and then the enable of VDD_CORE is pulled down; and VDD_CORE is sourced from the BUCK circuit, while VDDR_CORE is sourced from the LDO circuit. The power-down rate of VDD_CORE is very fast.

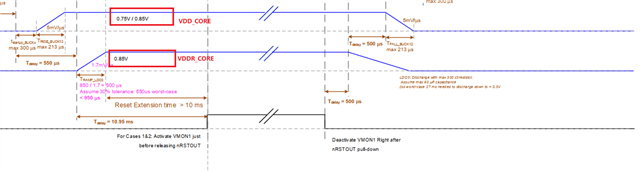

The following is the OTP timing diagram of TPS65224 combined with AM62A7. It can be seen that the power-down timing of OTP also fails to meet the required timing specified in the AM62A7 manual.

My questions are as follows:

1.During the power-on phase, meeting this requirement is quite easy. However, during the power-off phase, I wonder why it is necessary for VDDR_CORE to be completely powered off earlier than VDD_CORE, because these two actually can share the same power supply 0V85.

2.Based on my current power supply design, this requirement cannot be met. What impact will it have on my system? Do I need to modify the circuit to meet the timing requirements at this time?

Thank you for your help.

Xiwen