Tool/software:

I am implementing USB peripheral operation.

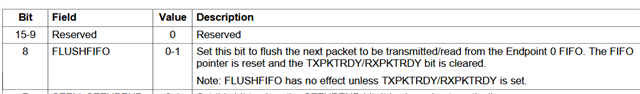

When flushing the receive endpoint FIFO with double buffering enabled, the specification document (spruh73q.pdf) states that it may be necessary to write the FLUSHFIFO bit in the PERI_RXCSR register twice.

However, observing the actual behavior, both buffers'data is being erased with a single write operation.

(After receiving two packets from the PC and then performing a single write to FLUSHFIFO, all data is gone.)

Is this the intended behavior? Also, does performing a second write afterward cause an extra FLUSH to occur?

best regards,