Other Parts Discussed in Thread: SYSBIOS

Tool/software:

Hi,

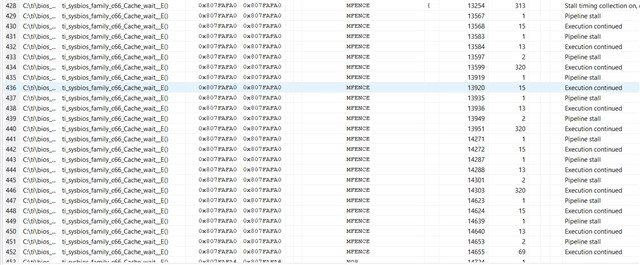

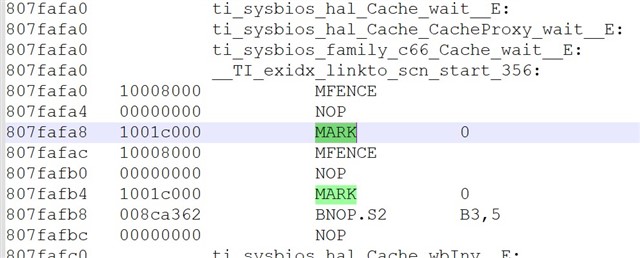

I'm on DSP1 collecting hardware trace flow, with PC and Cycle time.

What's the reason of these multiples wait?

Why there are tracing instructions left in?

I'm using:

SYSBIOS bios_6_83_00_18

xdctools_3_61_02_27_core

ccs1040

Thanks