Tool/software:

Hello TI Team,

Processor: AM6442

SDK Version: AM64x MCU+ SDK 11.00.00

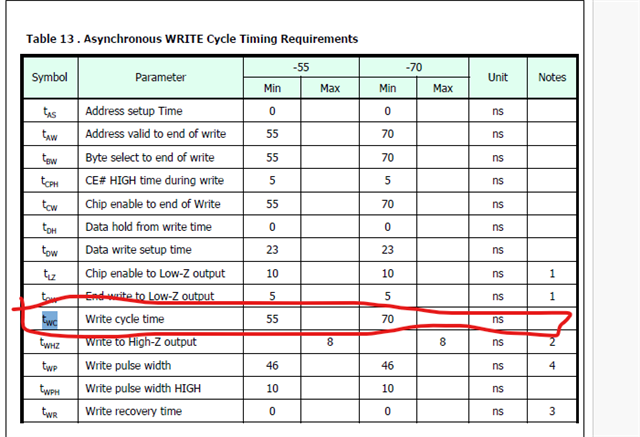

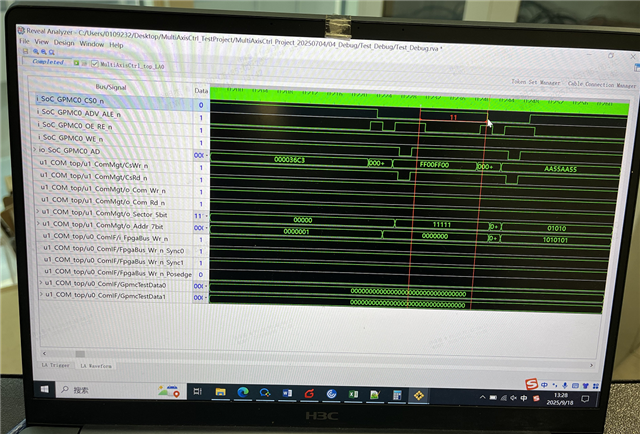

I am currently working with the AM6442 processor on a board, focusing on communication between R5F core and RAM through GPMC. When I use asynchronous single-write access on an Address/Data-Multiplexed device, the interval time between two nCS signals(Two writes) is 11 clock cycle(although I have already set the cycle2cycledelay parameters to 2), what parameters can I adjust to reduce the time interval to 2 clock cycles.

Please provide your inputs on this

Thanks and regards