Other Parts Discussed in Thread: AM62P

Tool/software:

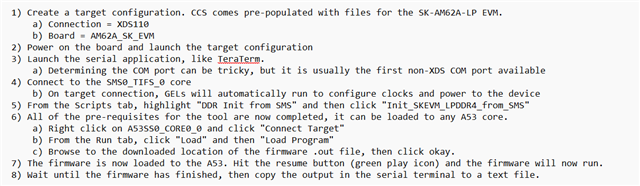

Hello, I´m trying to run the DDR margin firmware on the SK-AM62P-LP EVM through the JTAG interface using CCS, but following the readme file I got stuck on the four step:

4) Connect to the SMS0_TIFS_0 core

a) On target connection, GELs will automatically run to configure clocks and power to the device

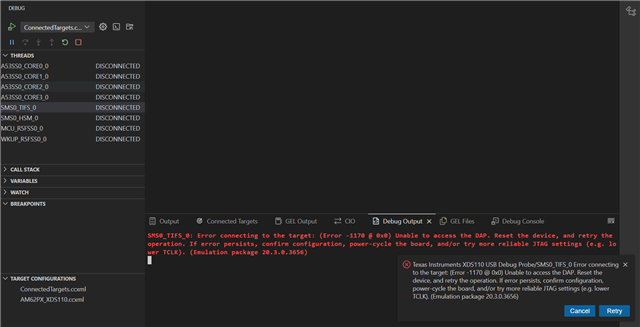

When I try to connect to this core, the following message pop up:

The error remain even after a reset and board power-cycle.

The boot mode on the board is OSPI NOR

I would like to get some support from you guys, the GEL file I´m using is the one embedded on the CCS Version: 20.3.0.14__1.9.0

C:\ti\ccs2002\ccs\ccs_base\emulation\gel\AM62P\

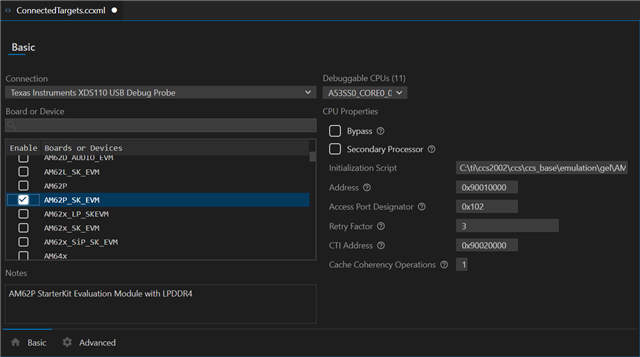

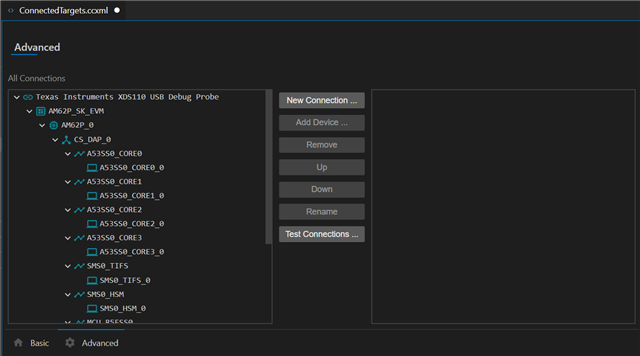

And the following .ccxml default configuration:

The debug session allow me to connect all cores but SMS0_TIFS_0 and SMS0_HSM_0.

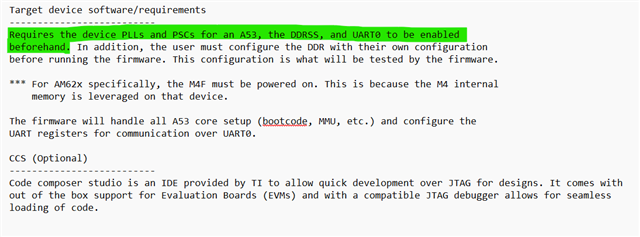

Another question, should I need to configure the UART0 channel on a GEL file to have the output of the firmware, since the readme file first say this:

but then: