Other Parts Discussed in Thread: AM62A7, TPS65224

Tool/software:

Hi,

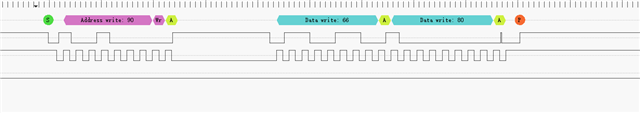

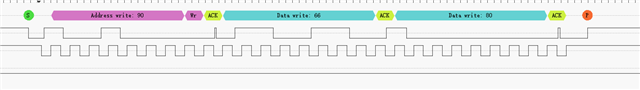

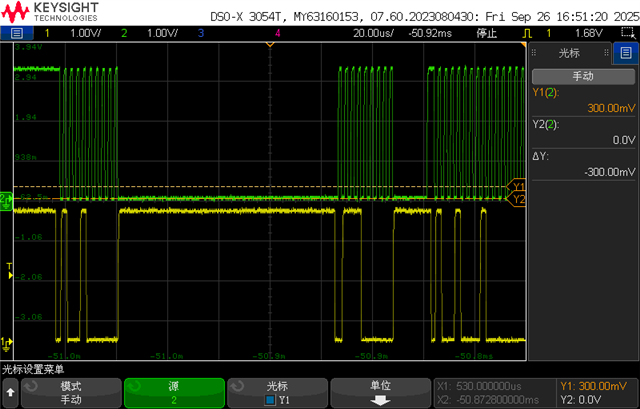

During the operation of our program, we have observed that the I2C signals sent by the main control chip occasionally experience timeout issues. This problem causes our program to return errors. Preliminary investigation suggests that the waveform generated by the I2C is abnormal

The captured erroneous signal image is as follows.