Other Parts Discussed in Thread: AM4376,

Tool/software:

Hello,

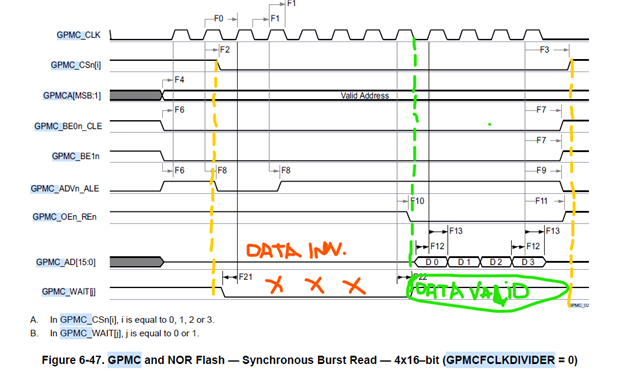

We have the GPMC interface connected to our ASIC via a 16 bit bus with wait acknowledgment. Everything appears to work great except for this one minor issue with excessive time between two U16 reads.

Data transfers that works great are as follows:

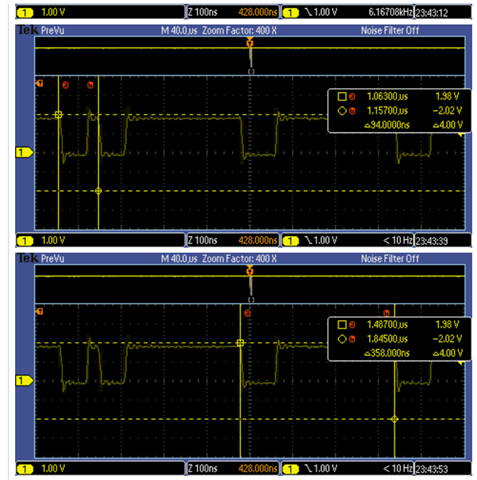

When the CPU requests a single U32 read or a U32 write, then the bus has 2 U16 transactions separated by less than 40 ns.

When the CPU requests a U16 write followed by a U16 write, then the bus has 2 U16 transactions separated by less than 50 ns.

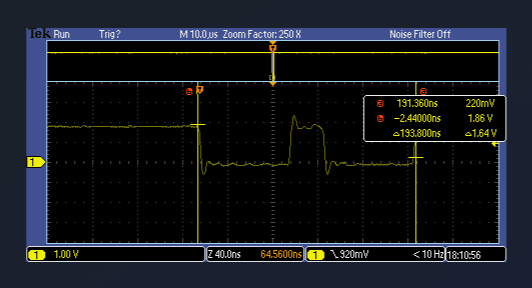

The problem is that when the CPU does a U16 read followed by another U16 read, then there is almost 250 ns of dead time between the accesses. Is there any way to improve this? I would expect the CPU to take the approximately the same 50ns separation between the two U16 reads that it would take to do the two separate U16 writes.