Tool/software:

Hi experts,

Previously, we have successfully output BT656 format images through DPI0.

Now, we plan to switch the output to DPI1 while keeping all other settings unchanged.

Based on the above case, I have made the following modifications.

1.In the file app_dss_defaults.c, the value of nodeDpiId has changed to APP_DCTRL_NODE_DPI_DPI1.

2.In the J721E_pinmux_data.c file, the pinmux configuration for Vout1 has been added.

static pinmuxPerCfg_t gVout0PinCfg[] =

{

/* MyVOUT0 -> VOUT0_DATA2 -> AF23 */

{

PIN_PRG1_PRU1_GPO2, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA3 -> AD23 */

{

PIN_PRG1_PRU1_GPO3, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA4 -> AH24 */

{

PIN_PRG1_PRU1_GPO4, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA5 -> AG21 */

{

PIN_PRG1_PRU1_GPO5, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA6 -> AE23 */

{

PIN_PRG1_PRU1_GPO6, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA7 -> AC21 */

{

PIN_PRG1_PRU1_GPO7, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA8 -> Y23 */

{

PIN_PRG1_PRU1_GPO8, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_DATA9 -> AF21 */

{

PIN_PRG1_PRU1_GPO9, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_HSYNC -> AJ26 */

{

PIN_PRG1_PRU1_GPO16, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_PCLK -> AH22 */

{

PIN_PRG1_PRU1_GPO19, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT0 -> VOUT0_VSYNC -> AJ22 */

{

PIN_PRG1_PRU1_GPO18, PIN_MODE(10) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

{PINMUX_END}

};

static pinmuxPerCfg_t gVout1PinCfg[] =

{

/* MyVOUT1 -> VOUT1_DATA2 -> V28 */

{

PIN_RGMII5_TD3, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA3 -> V29 */

{

PIN_RGMII5_TD2, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA4 -> V27 */

{

PIN_RGMII5_TD1, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA5 -> U28 */

{

PIN_RGMII5_TD0, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA6 -> U29 */

{

PIN_RGMII5_TXC, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA7 -> U25 */

{

PIN_RGMII5_RXC, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA8 -> U27 */

{

PIN_RGMII5_RD3, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_DATA9 -> U24 */

{

PIN_RGMII5_RD2, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_HSYNC -> W27 */

{

PIN_RGMII6_TD0, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_PCLK -> W29 */

{

PIN_RGMII6_TXC, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

/* MyVOUT1 -> VOUT1_VSYNC -> V25 */

{

PIN_RGMII6_TD1, PIN_MODE(4) | \

((PIN_PULL_DISABLE) & (~PIN_PULL_DIRECTION & ~PIN_INPUT_ENABLE))

},

{PINMUX_END}

};

static pinmuxModuleCfg_t gVoutPinCfg[] =

{

{0, TRUE, gVout0PinCfg},

{1, TRUE, gVout1PinCfg},

{PINMUX_END}

};

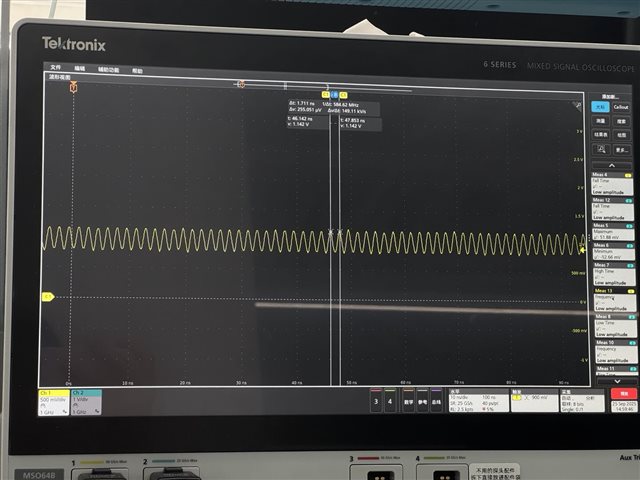

However, when switching to DPI1, I found that the PCLK waveform of Vout1 was very strange. The waveform diagram is shown below.

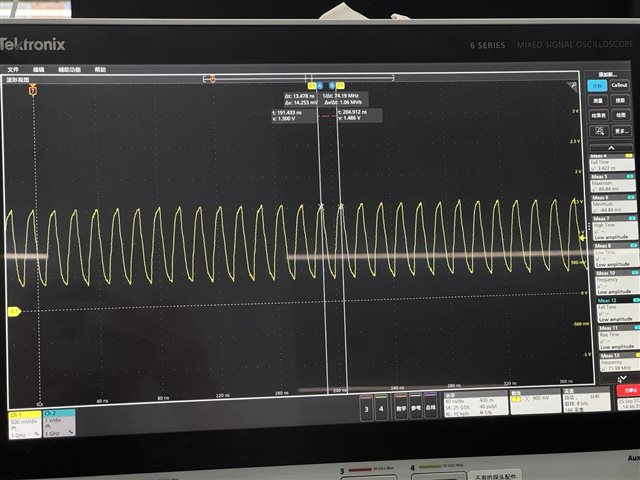

When I switch back to DPI0 again, I find that the PCLK waveform for Vout0 looks pretty good.The waveform diagram is shown below.

Could you please help me confirm if there were any omissions in my modifications that caused PCLK anomaly?

Thank you!