Tool/software:

Hello,

We want to use the custom board of the AM62L to perform read and write operations to the MRAM via OSPI.

Processor SDK version is 11.00.15.05. Our device tree file is as follows.

&ospi0 {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mram_pins_default>;

mram: s3a4004r0m@0 {

compatible = "netsol,s3a4004r0m", "jedec,spi-nor";

reg = <0>;

spi-tx-bus-width = <4>;

spi-rx-bus-width = <4>;

spi-max-frequency = <25000000>; /* 25MHz */

cdns,read-delay = <4>;

cdns,tshsl-ns = <60>;

cdns,tsd2d-ns = <60>;

cdns,tchsh-ns = <60>;

cdns,tslch-ns = <60>;

};

};

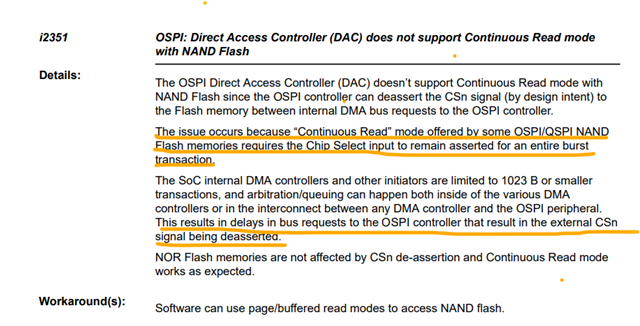

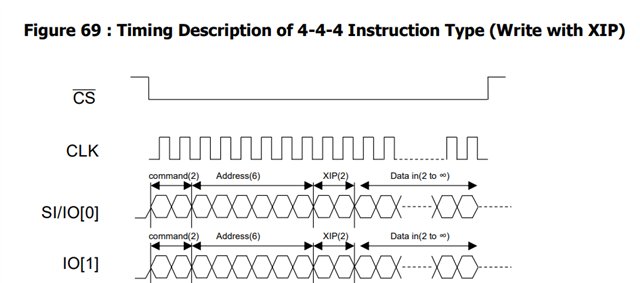

The datasheet of the MRAM we want to use requires that the CS remains asserted throughout a single transaction until it is completed.

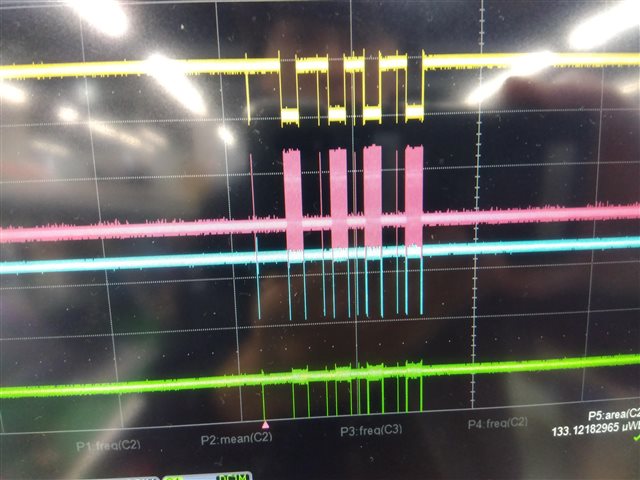

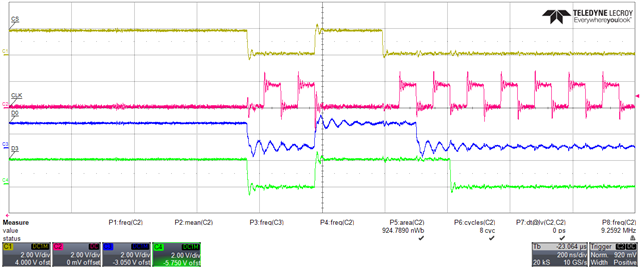

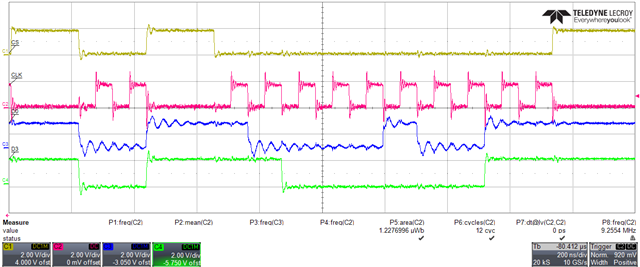

However, the actual waveform output from the custom board is as follows.

- After the command, the CS is turned OFF once.

- After the data transmission, the next command and address are immediately sent out.

- Then no data is sent, there is a waiting period, followed by sending the command again, waiting again, then sending the command, address, and data.

This difference causes problems with writing,

Even though I intended to write zeros to mtd0, 0xa5 is written at every 256-byte boundary.

dd if=/dev/zero bs=1024 count=1 | tr "\000" "\377" > test.bin dd if=./test.bin of=/dev/mtd0 bs=1024 count=1

# hexdump /dev/mtd0 0000000 ffff ffff ffff ffff ffff ffff ffff ffff * 00000f0 ffff ffff ffff ffff ffff ffff ffff a5ff 0000100 ffff ffff ffff ffff ffff ffff ffff ffff * 00001f0 ffff ffff ffff ffff ffff ffff ffff a5ff 0000200 ffff ffff ffff ffff ffff ffff ffff ffff * 00002f0 ffff ffff ffff ffff ffff ffff ffff a5ff 0000300 ffff ffff ffff ffff ffff ffff ffff ffff * 00003f0 ffff ffff ffff ffff ffff ffff ffff a5ff 0000400

I think the driver needs to be modified; how should I go about doing this?

Best regards,

Takayuki