Part Number: TDA4VM

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello,

I have a question regarding the Dio handling using the MCUSW_01_03_00_10_CONFIG

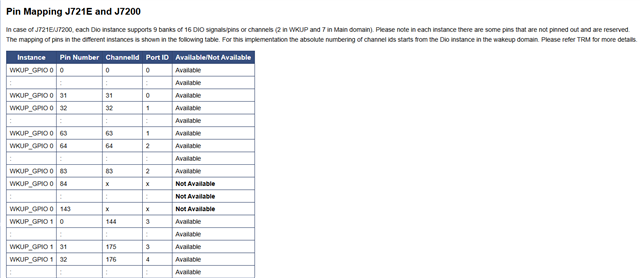

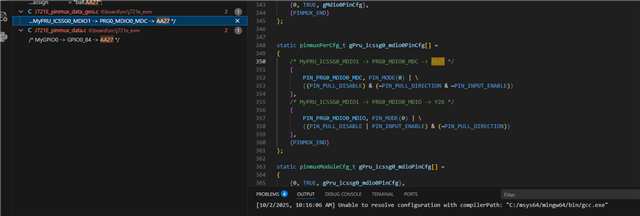

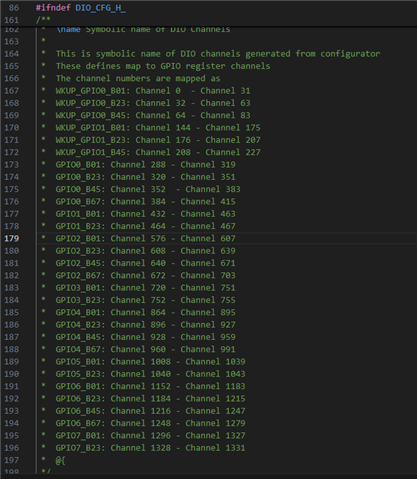

I can see Dio preconfigured but in a generation output I can see header and commens saying that there shall be more Ports and Channels defined:

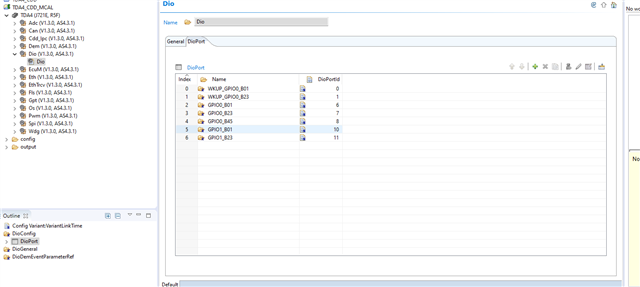

And these are the only ones defined:

If I want to use Port 0 Pin 81 i.e. currently I don't have that channel defined in the output.

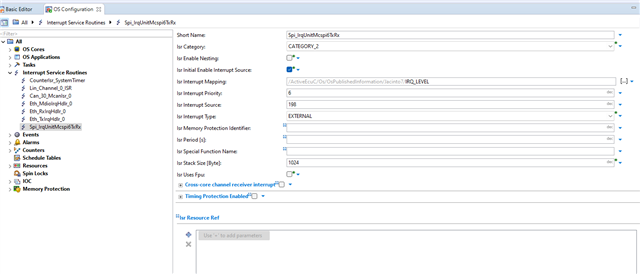

Do you know if this is expected for me to fill in by myself, I mean all other banks and channels or just this .xdm is not complete one? How i.e. Port 0, Pin 81 is expected to be defined or there is some calculation behind and I should find it under existing definitions (just to mention there is no Channel ID 81 in any of these).

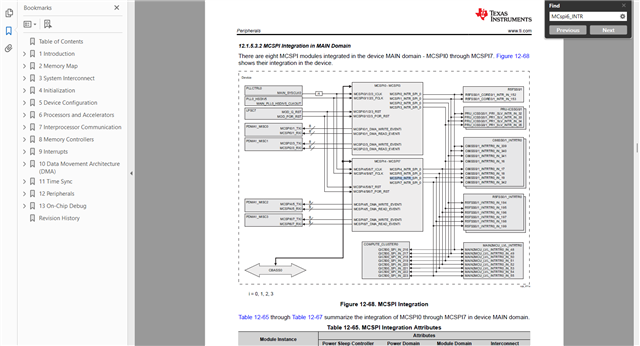

And I need that specific one Port 0, Pin 81 because I have application already existing but based on TI drivers and not ASR stack.

Do you know where could I find .xdm or .arxml with all of them for this target so I can integrate it more easily into Vector DaVinci Configurator?

Best Regards,

Tomislav