Other Parts Discussed in Thread: TEST2

Tool/software:

Hi Ti expert

SDK 0902

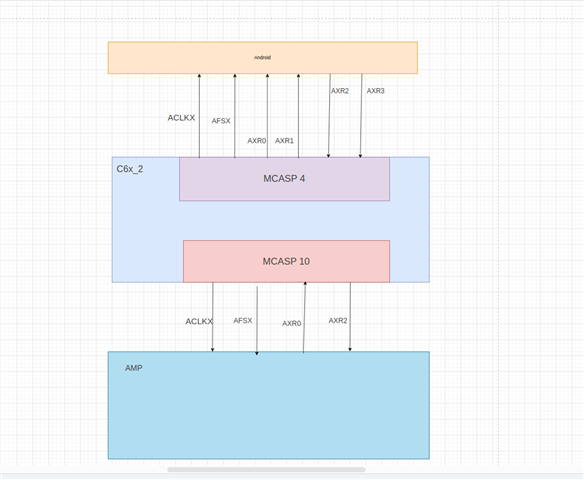

Hello expert Ti, I now have the following design for the audio:

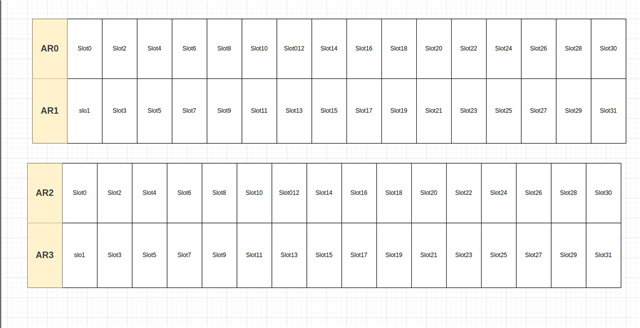

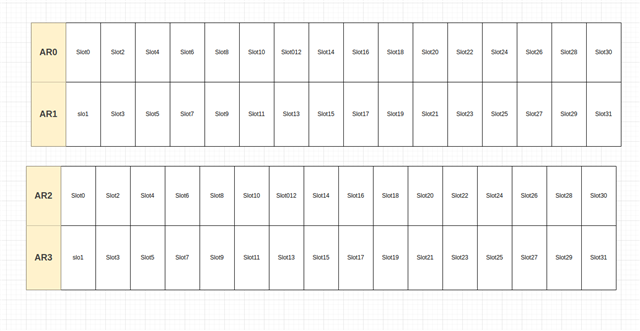

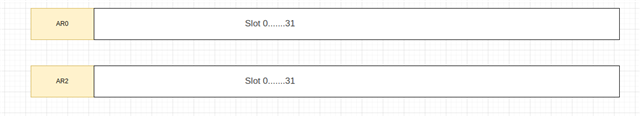

The C6x_2 to Android uses TDM32, with a slot size of 32 bits:

The C6x_2 to AMP uses TDM32, with a slot size of 32 bits.

《Q1》:

Actually, the slot size transmitted from the AMP is 24 bits (effective data is 16 bits).

However, from what I've seen, I can directly receive it using int32_t, and the audio data is not distorted. (I saved it for later review.)

However, when I send int32_t data from the C6x_2 to the Android, the audio is distorted. Furthermore, when the Android sends audio data (slot size is 24 bits, effective data is 16 bits, and the C6x_2 receives it using int32_t) to the C6x_2, the audio is also distorted.

All MCASP configuration options are identical between MCASP 4 and MCASP 10, except for the MCASP_TXFMCTL.FXWID field. (MCASP 4 uses a single word; MCASP 10 uses a single bit.)

(Attached is my configuration file).

《Q2》:

Clock configuration for mcasp10:

Sync clock: 48 kHz

Bit clock: 32 * 32 * 48 kHz = 49152000 Hz

I tested two clock configurations for mcasp4:

Sync clock: 48 kHz

Bit clock_test1: 16 * 32 * 48 kHz = 24576000 Hz

Bit clock_test2: 32 * 32 * 48 kHz = 49152000 Hz

Which bit clock is correct in mcasp4?

《Q3》:

In mcasp4, I only want to use a slot size of 32, so how do I configure bit padding and rotation?

Best Regards

Eason

/*

* mcasp_cfg.c

*

* This file contains the test / demo code to demonstrate the Audio component

* driver functionality on SYS/BIOS 6.

*

* Copyright (C) 2009-2017 Texas Instruments Incorporated - http://www.ti.com/

*

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions

* are met:

*

* Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

*

* Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the

* distribution.

*

* Neither the name of Texas Instruments Incorporated nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

* "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

* LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

* A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

* OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

* SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

* LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

* DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

* THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

* OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

*

*/

/** \file mcasp_cfg.c

*

* \brief sample application for demostration of audio playing

*

* This file contains the implementation of the sample appliation for the

* demonstration of audio playing through the audio interface layer.

*

* (C) Copyright 2009, Texas Instruments, Inc

*/

/* ========================================================================== */

/* INCLUDE FILES */

/* ========================================================================== */

#if defined (USE_BIOS)

#include <xdc/std.h>

#include <ti/sysbios/io/IOM.h>

#include <xdc/runtime/Memory.h>

#include <ti/sysbios/heaps/HeapMem.h>

#include <xdc/runtime/IHeap.h>

#include <xdc/runtime/Error.h>

#include <xdc/runtime/Log.h>

#include <xdc/runtime/System.h>

#include <ti/sysbios/BIOS.h>

#include <ti/sysbios/knl/Semaphore.h>

#endif /* USE BIOS */

#include <ti/drv/mcasp/mcasp_osal.h>

#include <ti/drv/mcasp/soc/mcasp_soc.h>

#include "stdio.h"

#include "string.h"

#include "autox_dsp_audio_app.h"

#include "autox_dsp_audio_fmt.h"

#include <ti/drv/sciclient/soc/sysfw/include/j721e/tisci_devices.h>

#include <ti/drv/sciclient/soc/sysfw/include/j721e/tisci_clocks.h>

#include <ti/drv/sciclient/sciclient.h>

#include <ti/board/src/j721e_evm/J721E_pinmux.h>

#include <ti/board/board.h>

#include <ti/board/src/j721e_evm/include/board_pinmux.h>

#include <ti/board/src/j721e_evm/include/board_cfg.h>

#include <ti/board/src/j721e_evm/include/board_clock.h>

#include <ti/csl/hw_types.h>

#include <ti/csl/src/ip/rat/V0/cslr_rat.h>

#include <ti/csl/src/ip/rat/V0/csl_rat.h>

#include <ti/drv/mcasp/mcasp_osal.h>

#include <ti/drv/mcasp/soc/mcasp_soc.h>

#include <ti/drv/mcasp/include/McaspLocal.h>

#include "app_log.h"

void GblErrXmt0(Mcasp_errCbStatus errCbStat);

void GblErrRcv0(Mcasp_errCbStatus errCbStat);

void GblErrXmt4(Mcasp_errCbStatus errCbStat);

void GblErrRcv4(Mcasp_errCbStatus errCbStat);

/* ========================================================================== */

/* IMPORTED VARIABLES */

/* ========================================================================== */

/* ========================================================================== */

/* McASP Init config */

/* ========================================================================== */

static Mcasp_HwSetupData mcasp10RcvSetup =

{

/* .rmask = */ 0xFFFFFFFF, /* All the data bits are to be used */

/* .rfmt = */ 0x000080F0, /* 0/1 bit delay from framsync

* MSB first

* No extra bit padding

* Padding bit (ignore)

* slot Size is 32

* Reads from DMA port

* NO rotation

*/

/* .afsrctl = */ 0x00001103, /* 17 SLOTS,

* Frame sync is one word

* Internally generated frame sync

* Falling edge is start of frame

*/

/* .rtdm = */ 0xFFFFFFFF, /* 32 slots are active (TDM32) */

/* .rintctl = */ 0x00000003, /* sync error and overrun error */

/* .rstat = */ 0x000001FF, /* reset any existing status bits */

/* .revtctl = */ 0x00000000, /* DMA request is enabled or disabled */

{

/* .aclkrctl = */ 0x000000A3, /* Div (8), Internal Source, rising edge */

/* .ahclkrctl = */ 0x00008010, /* Div (20), Internal AUX_CLK Source */

/* .rclkchk = */ 0x00000000

}

};

static Mcasp_HwSetupData mcasp10XmtSetup =

{

/* .xmask = */

0xFFFFFFFF, /* All the data bits are to be used */

/* .xfmt = */ 0x000080F0, /* 0/1 bit delay from framsync

* MSB first

* No extra bit padding

* Padding bit (ignore)

* slot Size is 32

* Reads from DMA port

* 0-bit rotation

*/

/* .afsxctl = */ 0x00001103, /* I2S mode,

* Frame sync is one word

* internally generated frame sync

* Falling edge is start of frame

*/

/* .xtdm = */ 0xFFFFFFFF, /* 32 slots are active (TDM32) */

/* .xintctl = */ 0x00000003, /* sync error,overrun error,clK error */

/* .xstat = */ 0x000001FF, /* reset any existing status bits */

/* .xevtctl = */ 0x00000000, /* DMA request is enabled or disabled */

{

/* .aclkxctl = */ 0x000000A3, /* Div (8), Internal Source, SYNC, Falling edge */

/* .ahclkxctl = */ 0x00008010, /* Div (20), Internal AUX_CLK Source */

/* .xclkchk = */ 0x00000000

},

};

/* McAsp channel parameters */

static Mcasp_ChanParams mcaspAmpChanParam[2] =

{

{

1,//RX_NUM_SERIALIZER, /* number of serialisers */

{Mcasp_SerializerNum_0}, /* serialiser index */

&mcasp10RcvSetup,

TRUE,

Mcasp_OpMode_TDM, /* Mode (TDM/DIT) */

Mcasp_WordLength_32,

NULL,

0,

NULL,

(Mcasp_GblCallback) &GblErrRcv0,

32, /* number of TDM channels */

Mcasp_BufferFormat_1SER_MULTISLOT_INTERLEAVED,

TRUE,

1, /* RX_FIFO_EVENT_DMA_RATIO */

TRUE,

Mcasp_WordBitsSelect_MSB

},

{

1, /* number of serialisers */

{Mcasp_SerializerNum_2}, /* serialiser index */

&mcasp10XmtSetup,

TRUE,

Mcasp_OpMode_TDM,

Mcasp_WordLength_32, /* word width */

NULL,

0,

NULL,

(Mcasp_GblCallback) &GblErrXmt0,

32, /* number of TDM channels */

Mcasp_BufferFormat_1SER_MULTISLOT_INTERLEAVED,

TRUE,

1, /* TX_FIFO_EVENT_DMA_RATIO */

TRUE,

Mcasp_WordBitsSelect_MSB

}

};

static Mcasp_HwSetupData mcasp04RcvSetup =

{

/* .rmask = */

0xFFFFFFFF, /* All the data bits are to be used */

/* MCASP_RXFMT */

/* .rfmt = */ 0x000080F0, /* 0/1 bit delay from framsync

* MSB first

* No extra bit padding

* Padding bit (ignore)

* slot Size is 32

* Reads from DMA port

* NO rotation

*/

/* MCASP_RXFMCTL */

/* .afsrctl = */ 0x000001011, /* TDM32 (32 SLOTS)

* Frame sync is one word

* Externally generated frame sync

* Falling edge is start of frame

*/

/* MCASP_RXTDM */

/* .rtdm = */ 0xFFFFFFFF, /* 32 slots are active (TDM32) */

/* .rintctl = */ 0x00000003, /* sync error and overrun error */

/* .rstat = */ 0x000001FF, /* reset any existing status bits */

/* .revtctl = */ 0x00000000, /* DMA request is enabled or disabled */

{

/* .ahclkrctl = */ 0x00008010, /* Div (17), Internal AUX_CLK Source

CPU Clock passed through divider. Divider output on AHCLKR pin.*/

/* .rclkchk = */ 0x00000000

}

};

static Mcasp_HwSetupData mcasp04XmtSetup =

{

/* .xmask = */

0xFFFFFFFF, /* All the data bits are to be used */

/* .xfmt = */ 0x000080F0, /* 0/1 bit delay from framsync

* MSB first

* No extra bit padding

* Padding bit (ignore)

* slot Size is 32

* Reads from DMA port

* 0-bit rotation

*/

/* MCASP_TXFMCTL */

/* .afsxctl = */ 0x000001011, /* TDM32 mode,

* Frame sync is one word

* Internally-generated transmit frame sync..

* Falling edge is start of frame

*/

/* .xtdm = */ 0xFFFFFFFF, /* 32 slots are active (TDM32) */

/* .xintctl = */ 0x00000003, /* sync error,overrun error,clK error */

/* .xstat = */ 0x000001FF, /* reset any existing status bits */

/* .xevtctl = */ 0x00000000, /* DMA request is enabled or disabled */

{

/* .aclkxctl = */ 0x000000A3, /* Div (8), Internal Source, SYNC, Falling edge */

/* .ahclkxctl = */ 0x00008010, /* Div (20), Internal AUX_CLK Source */

/* .xclkchk = */ 0x00000000

},

};

/* McAsp channel parameters */

static Mcasp_ChanParams mcaspCdcChanParam[2] =

{

{

2, /* number of serialisers */

{Mcasp_SerializerNum_2, Mcasp_SerializerNum_3}, /* serialiser index */

&mcasp04RcvSetup,

TRUE,

Mcasp_OpMode_TDM, /* Mode (TDM/DIT) */

Mcasp_WordLength_32,

NULL,

0,

NULL,

(Mcasp_GblCallback) &GblErrRcv4,

32, /* number of TDM channels */

Mcasp_BufferFormat_MULTISER_MULTISLOT_SEMI_INTERLEAVED_1,

TRUE,

1, /* RX_FIFO_EVENT_DMA_RATIO */

TRUE,

Mcasp_WordBitsSelect_MSB

},

{

2, /* number of serialisers */

{Mcasp_SerializerNum_0, Mcasp_SerializerNum_1}, /* serialiser index */

&mcasp04XmtSetup,

TRUE,

Mcasp_OpMode_TDM,

Mcasp_WordLength_32, /* word width */

NULL,

0,

NULL,

(Mcasp_GblCallback) &GblErrXmt4,

32,

Mcasp_BufferFormat_MULTISER_MULTISLOT_SEMI_INTERLEAVED_1,

TRUE,

1, /* TX_FIFO_EVENT_DMA_RATIO */

TRUE,

Mcasp_WordBitsSelect_MSB

}

};

void mcaspGetPortParam(uint32_t port, void **rx, void **tx)

{

if (port == MCASP10_PORT_AMP)

{

*rx = &mcaspAmpChanParam[0];

*tx = &mcaspAmpChanParam[1];

}

else if (port == MCASP04_PORT_CDC)

{

*rx = &mcaspCdcChanParam[0];

*tx = &mcaspCdcChanParam[1];

}

}

void mcaspPortClockSet(uint32_t port)

{

uint64_t freq = 0;

if (port == MCASP10_PORT_AMP)

{

/* McASP0 AUXCLK selects MAIN_PLL4_HSDIV0_CLKOUT */

Sciclient_pmSetModuleClkParent(TISCI_DEV_MCASP10,

TISCI_DEV_MCASP10_AUX_CLK,

TISCI_DEV_MCASP10_AUX_CLK_PARENT_HSDIV3_16FFT_MAIN_4_HSDIVOUT0_CLK,

SCICLIENT_SERVICE_WAIT_FOREVER);

/* Set AUXCLK as 49152000 hz */

if (Sciclient_pmSetModuleClkFreq(TISCI_DEV_MCASP10,

TISCI_DEV_MCASP10_AUX_CLK,

49152000,

0,

SCICLIENT_SERVICE_WAIT_FOREVER) != CSL_PASS)

{

log("set freq error\n");

}

if (Sciclient_pmGetModuleClkFreq(TISCI_DEV_MCASP10,

TISCI_DEV_MCASP10_AUX_CLK,

&freq,

SCICLIENT_SERVICE_WAIT_FOREVER) == CSL_PASS)

{

log("mcasp %d aux clk freq = %lld\n", port, freq);

}

}

if (port == MCASP04_PORT_CDC)

{

/* McASP0 AUXCLK selects MAIN_PLL4_HSDIV0_CLKOUT */

Sciclient_pmSetModuleClkParent(TISCI_DEV_MCASP4,

TISCI_DEV_MCASP4_AUX_CLK,

TISCI_DEV_MCASP4_AUX_CLK_PARENT_HSDIV3_16FFT_MAIN_4_HSDIVOUT0_CLK,

SCICLIENT_SERVICE_WAIT_FOREVER);

/* Set AUXCLK as 49152000 hz */

if (Sciclient_pmSetModuleClkFreq(TISCI_DEV_MCASP4,

TISCI_DEV_MCASP4_AUX_CLK,

49152000,

0,

SCICLIENT_SERVICE_WAIT_FOREVER) != CSL_PASS)

{

log("set freq error\n");

}

if (Sciclient_pmGetModuleClkFreq(TISCI_DEV_MCASP4,

TISCI_DEV_MCASP4_AUX_CLK,

&freq,

SCICLIENT_SERVICE_WAIT_FOREVER) == CSL_PASS)

{

log("mcasp 4 aux clk freq = %lld\n", freq);

}

}

}

#define TDA4_TDM_MASTER

#define AUTOX_AUDIO_CDC_VER_1_1

static void testBoard_pinmuxWriteProxy1Reg(uint8_t domain,

uint32_t baseAddr,

uint32_t regVal)

{

uint32_t claimAddr;

uint32_t claimOffset;

uint32_t claimShift;

uint32_t claimRegVal;

if(BOARD_SOC_DOMAIN_MAIN == domain)

{

claimAddr = BOARD_MAIN_MMR_P7_CLAIM_ADDR;

/* Get the register offset from base of P7 claim offset range */

claimOffset = (baseAddr - BOARD_MAIN_PMUX_CTRL_ADDR);

}

else

{

claimAddr = BOARD_WKUP_MMR_P7_CLAIM_ADDR;

/* Get the register offset from base of P7 claim offset range */

claimOffset = (baseAddr - BOARD_WKUP_PMUX_CTRL_ADDR);

}

/* Each claim register configures 128 byte address range.

Calculate the register offset for P7 claim register block and

and shift values within the claim register */

claimShift = claimOffset % BOARD_MMR_CLAIM_ADDR_PER_REG;

claimOffset = claimOffset / BOARD_MMR_CLAIM_ADDR_PER_REG;

claimRegVal = HW_RD_REG32((claimAddr + (4*claimOffset)));

claimRegVal |= (1U << claimShift);

/* Claim the register access */

HW_WR_REG32((claimAddr + (4*claimOffset)), claimRegVal);

/* Write PAD config MMR register */

HW_WR_REG32(baseAddr, regVal);

}

static uint32_t testBoard_pinmuxGetBaseAddr(uint8_t domain)

{

uint32_t baseAddr;

switch(domain)

{

case BOARD_SOC_DOMAIN_MAIN:

baseAddr = BOARD_MAIN_PMUX_CTRL_ADDR;

break;

case BOARD_SOC_DOMAIN_WKUP:

baseAddr = BOARD_WKUP_PMUX_CTRL_ADDR;

break;

default:

baseAddr = 0U;

break;

}

return baseAddr;

}

static void testBoard_pinmuxSetReg(uint8_t domain,

uint32_t offset,

uint32_t muxData)

{

uint32_t baseAddr;

baseAddr = testBoard_pinmuxGetBaseAddr(domain);

testBoard_pinmuxWriteProxy1Reg(domain,

(baseAddr + offset),

muxData);

}

void mcaspPinMuxSet()

{

uint32_t reg = 0;

/*c66 can not access ctrl mmr cfg address directly, need translation here.*/

{

CSL_ratRegs *pC66xRatRegs = (CSL_ratRegs *)CSL_C66_COREPAC_C66_RATCFG_BASE;

CSL_RatTranslationCfgInfo TranslationCfg;

TranslationCfg.sizeInBytes = CSL_CTRL_MMR0_CFG0_SIZE;

TranslationCfg.baseAddress = CSL_CTRL_MMR0_CFG0_BASE +

CSL_C66_COREPAC_RAT_REGION_BASE;

TranslationCfg.translatedAddress = CSL_CTRL_MMR0_CFG0_BASE;

/* We use RAT region 0 for CSL_GPIO0_BASE address translation */

if (CSL_ratIsRegionTranslationEnabled(pC66xRatRegs, 0) == (bool)false)

{

CSL_ratEnableRegionTranslation(pC66xRatRegs, 0);

CSL_ratConfigRegionTranslation(pC66xRatRegs, 0, &TranslationCfg);

}

}

{

/* MCASP10_ACLKX as mode 12*/

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_TX_CTL, 0x0000000C);

/* MCASP10_AFSX as mode 12 */

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_RX_CTL, 0x0000000C);

/* MCASP10_AXR0 as mode 12 Receiver enabled*/

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_TD3, 0x0004000C);

/* MCASP10_AXR2 as mode 12. */

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_TXC, 0x0000000C);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_TX_CTL, ®);

log("MCASP10_ACLKX --> %#x\n", reg);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_RX_CTL, ®);

log("MCASP10_AFSX --> %#x\n", reg);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_TD3, ®);

log("MCASP10_AXR0 --> %#x\n", reg);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_RGMII5_TXC, ®);

log("MCASP10_AXR2 --> %#x\n", reg);

}

{

/* MCASP4_ACLKX*/

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU0_GPO18, 0x0000000C);

/* MCASP4_AFSX*/

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU0_GPO19, 0x0000000C);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU0_GPO18, ®);

log("MCASP4_ACLKX --> %#x\n", reg);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU0_GPO19, ®);

log("MCASP4_AFSX --> %#x\n", reg);

/* MCASP4_AXR0 -> AG21 */

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO5, 0x0000000C);

/*MCASP4_AXR2 -> Y23 */

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO8, 0x0004000C);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO5, ®);

log("MCASP4_AXR0 --> %#x\n", reg);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO8, ®);

log("MCASP4_AXR2 --> %#x\n", reg);

/* MCASP4_AXR1 -> AC21 */

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO7, 0x0000000C);

/*MCASP4_AXR3 -> AF21 */

autoxBoard_pinmuxSetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO9, 0x0004000C);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO7, ®);

log("MCASP4_AXR1 --> %#x\n", reg);

Board_pinmuxGetReg(BOARD_SOC_DOMAIN_MAIN, PIN_PRG1_PRU1_GPO9, ®);

log("MCASP4_AXR3 --> %#x\n", reg);

}

}

void mcaspFmtCfg(uint32_t port, void *_para)

{

Mcasp_Params *para = _para;

ASSERT(NULL != para);

*para = Mcasp_PARAMS;

if (port == MCASP10_PORT_AMP)

{

/* MCASP_PDIR */

para->mcaspHwSetup.glb.pdir = 0xfc000004;

para->mcaspHwSetup.glb.pfunc = 0x0;

para->mcaspHwSetup.glb.ctl = 0x00001f1f;

para->mcaspHwSetup.glb.serSetup[0] = Mcasp_SerMode_RCV;

para->mcaspHwSetup.glb.serSetup[2] = Mcasp_SerMode_XMT;

/* MCASP_TXFMT */

para->mcaspHwSetup.tx.fmt = 0x000080f0;

/* MCASP_TXFMCTL */

para->mcaspHwSetup.tx.frSyncCtl = 0x00001002;

/* MCASP_TXTDM */

para->mcaspHwSetup.tx.tdm = 0xffffffff;

para->mcaspHwSetup.tx.intCtl = 0x3;

para->mcaspHwSetup.tx.stat = 0x1ff;

para->mcaspHwSetup.tx.evtCtl = 0;

para->mcaspHwSetup.tx.clk.clkSetupHiClk = 0x00008000;

para->mcaspHwSetup.tx.clk.clkSetupClk = 0x000000a0;

para->mcaspHwSetup.rx = para->mcaspHwSetup.tx;

mcaspAmpChanParam[1].mcaspSetup = ¶->mcaspHwSetup.tx;

mcaspAmpChanParam[0].mcaspSetup = ¶->mcaspHwSetup.rx;

}

/* tda4 as master... */

if (port == MCASP04_PORT_CDC)

{

/* MCASP_PDIR */

/**

* 1, AFSR as output.

* 2, AHCLKR as output.

* 3, ACLKR as output.

* 4, AFSX as output.

* 5, AHCLKX as output.

* 6, ACLKX as output.

* 7, AR0 AR1 as input, AR2 AR3 as output.

*/

para->mcaspHwSetup.glb.pdir = 0xfc00000C;

/* All pin as mcasp pin */

para->mcaspHwSetup.glb.pfunc = 0x0;

/**

* 1, Receive clock divider is running.

* 2, Receive high-frequency clock divider is running.

* 3, Receive serializers are active.

* 4, Receive state machine is released from reset.

* 5, Receive frame sync generator is active.

* 6, Transmit clock divider is running.

* 7, Transmit high-frequency clock divider is running.

* 8, Transmit serializers are active.

* 9, Transmit state machine is released from reset.

* 10, Transmit frame sync generator is active

*/

para->mcaspHwSetup.glb.ctl = 0x00001f1f;

/* In EP2: serializer 0 & 1 as TX

serializer 2 & 3 as RX */

para->mcaspHwSetup.glb.serSetup[0] = Mcasp_SerMode_XMT;

para->mcaspHwSetup.glb.serSetup[1] = Mcasp_SerMode_XMT;

para->mcaspHwSetup.glb.serSetup[2] = Mcasp_SerMode_RCV;

para->mcaspHwSetup.glb.serSetup[3] = Mcasp_SerMode_RCV;

/* Bit Stream Format Register */

/**

* 1, Slot size is 32 bits.

* 2, Bitstream is MSB first.

*/

para->mcaspHwSetup.tx.fmt = 0x000080f0; /* MCASP_TXFMT */

/* Frame Sync Control Register */

/**

* 1, A falling edge on transmit frame sync (AFSX)

* indicates the beginning of a frame

*

* 2, Internally-generated transmit frame sync.

* 3, Single word.

*/

para->mcaspHwSetup.tx.frSyncCtl = 0x00001013; /* MCASP_TXFMCTL */

/* slot 0 -> slot 32 is avtive */

para->mcaspHwSetup.tx.tdm = 0xFFFFFFFF; /* MCASP_TXTDM */

/**

* 1, Transmitter underrun interrupt enable bit

* 2, Unexpected transmit frame sync interrupt enable bit.

*/

para->mcaspHwSetup.tx.intCtl = 0x3; /* MCASP_EVTCTLX */

/**

* 1, Transmitter underrun did occur.

* 2, Unexpected transmit frame sync did occur.

* 3 ....

*/

para->mcaspHwSetup.tx.stat = 0x1ff; /* MCASP_TXSTAT */

/* Transmit data DMA request is enabled. */

para->mcaspHwSetup.tx.evtCtl = 0; /* MCASP_XEVTCTL */

/* Internal transmit high-frequency clock source from output of

programmable high clock divider. AUXCLK to AHCLKX: Divide-by-1 */

para->mcaspHwSetup.tx.clk.clkSetupHiClk = 0x00008000; /* MCASP_AHCLKXCTL */

/**

* 1, Transmit bit clock divide ratio bits determine the divide-down ratio

from AHCLKX to ACLKX. Divide-by-1

2, Internal transmit clock source from output of programmable bit

clock divider.

3, Falling edge. External receiver samples data on the rising edge

of the serial clock, so the transmitter must shift data out on the falling

edge of the serial clock.

*/

para->mcaspHwSetup.tx.clk.clkSetupClk = 0x000000A0; /* MCASP_ACLKXCTL */

/* All rx data enabled and returned to CPU or DMA */

para->mcaspHwSetup.rx.mask = 0xffffffff;

/* Bit Stream Format Register */

/**

* 1, Slot size is 32 bits.

* 2, Bitstream is MSB first.

*/

para->mcaspHwSetup.rx.fmt = 0x000080f0; /* MCASP_RXFMT */

/* Frame Sync Control Register */

/**

* 1, Internally-generated receive frame sync.

* 2, Receive Framee sync mode 32-slots TDM (TDM32)

* 3, Single word.

*/

para->mcaspHwSetup.rx.frSyncCtl = 0x00001012; /* MCASP_RXFMCTL */

/* SLOT 0 to SLOT32 */

para->mcaspHwSetup.rx.tdm = 0xFFFFFFFF; /* MCASP_RXTDM */

/**

* 1, Transmitter underrun interrupt enable bit

* 2, Unexpected transmit frame sync interrupt enable bit.

*/

para->mcaspHwSetup.rx.intCtl = 0x03; /* MCASP_EVTCTLX */

para->mcaspHwSetup.rx.stat = 0x1ff;

para->mcaspHwSetup.rx.evtCtl = 0;

/* Receive clock divide ratio from CPU master clock: Divide-by-2 */

para->mcaspHwSetup.rx.clk.clkSetupHiClk = 0x00008001; /* MCASP_AHCLKRCTL */

para->mcaspHwSetup.rx.clk.clkSetupClk = 0x000000A0; /* MCASP_ACLKRCTL */

para->mcaspHwSetup.rx.clk.clkChk = 0;

mcaspCdcChanParam[1].mcaspSetup = ¶->mcaspHwSetup.tx;

mcaspCdcChanParam[0].mcaspSetup = ¶->mcaspHwSetup.rx;

logd("Audio: MCASP_ACLKRCTL 0x%x\n", para->mcaspHwSetup.rx.clk.clkSetupClk);

logd("Audio: MCASP_PDIR 0x%x\n", para->mcaspHwSetup.glb.pdir);

}

}