Part Number: TDA4VM

Other Parts Discussed in Thread: SYSBIOS

Tool/software:

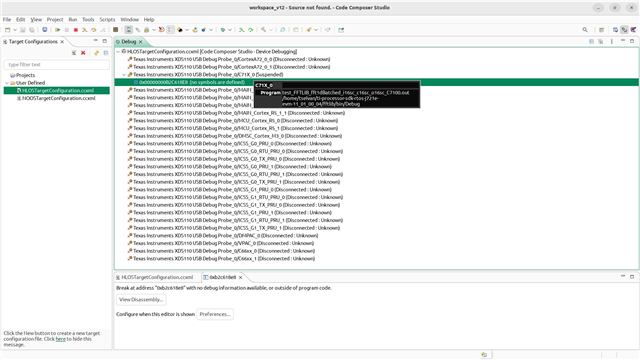

Board setup: J721EXSOMG01EVM + J721EXCP01EVM

Hello,

I am new to TDA4VM development and need some guidance. Our goal is to perform signal processing on the DSP cores (both C66x and C7x) and communicate with the ARM and DSP,R5F cores using IPC.

We are planning to use RTOS, but we noticed that SYS/BIOS is not provided for TDA4VM. I have the following questions:

-

How to create an RTOS-based CCS project for DSP and R5F?

-

We prefer this option because we have a little experience with SYS/BIOS, but we are open to other RTOS options.

-

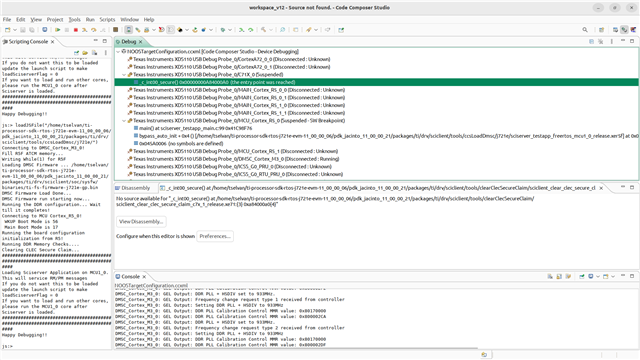

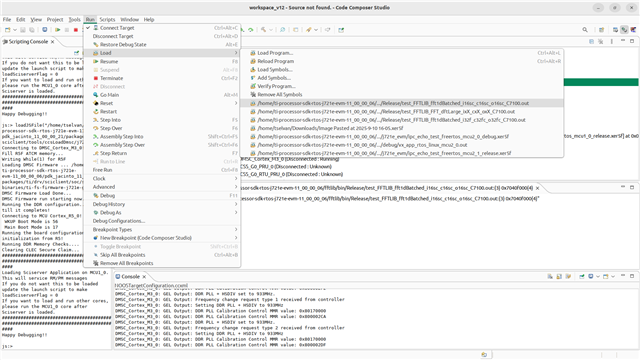

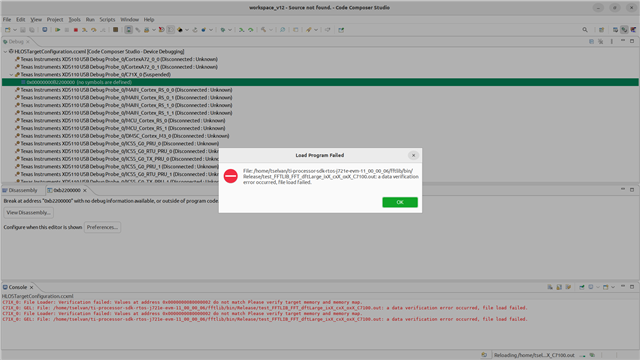

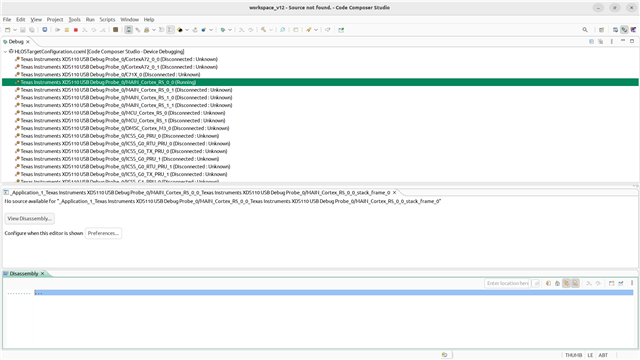

What is the recommended way to create, build, and debug such projects in CCS?

-

-

If RTOS/SYSBIOS is not possible:

-

Can we achieve signal processing using the Vision SDK (via CCS)?

-

If yes, what are the steps to build, load, and debug DSP/R5F code in CCS?

-

-

Why is SYS/BIOS not provided for TDA4VM?

-

What alternatives are available ?

-

How should we effectively use these alternatives for DSP and R5F development?

-

It would be very helpful if you can provide clear instructions with references to official documentation.

Thank you