Other Parts Discussed in Thread: OPA365-Q1

Tool/software:

Hi TI team,

I am working on VCM with Khemraj,

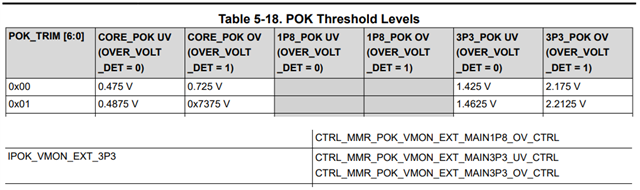

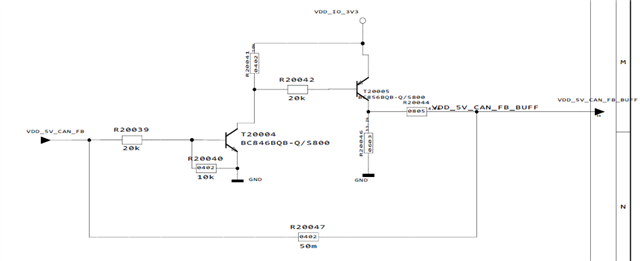

In our design we have implemented voltage monitor ckt at pin R29 pin of at SoC(TDA4VH88T5AALYRQ1) for monitoring 5V using external voltage divider as shown in below image.

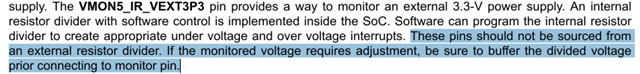

In datasheet for R29(VMON5_IR_VEXT3P3) its mentioned that :

1.) Its shouldn't be provided from external divider and if its provided then need to buffer the divided voltage.

----> Q-1) Is the provided configuration OK, or will it have issues?

The voltage divider network is provided with 5V,that will generate 3.516V which is under the pin max voltage limit (-0.3 to 3.8V)

---->Q-2) During transient conditions or in case of an operational fault, Input voltage to resistor divider rail may rise to 6 V instead of the nominal 5 V. Under such a condition, the current voltage divider configuration would output 4.219 V, which exceeds the maximum allowable voltage at the SoC pin.

If the SoC pin experiences 4.219 V, will it potentially damage the SoC pin, or is there any internal protection mechanism that would detect the over-voltage condition and transition the SoC into a cutoff or safe mode?

Please confirm if the configuration is OK, or do we need to change the resistor divider?