Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

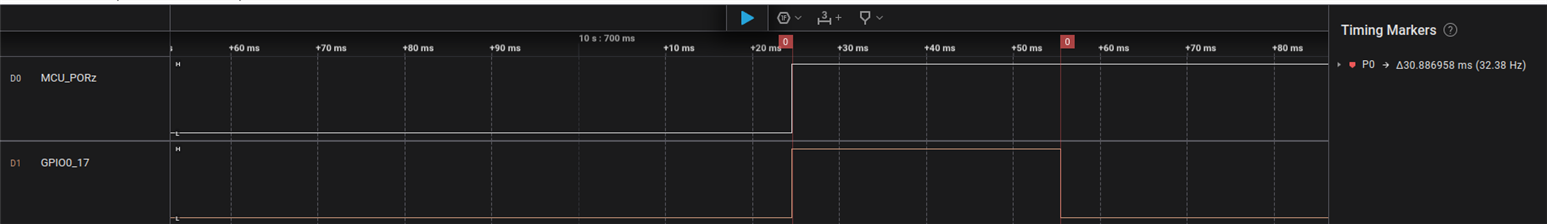

I want to achieve the fast boot in WKUP core and measured the corresponding time slots. The time measurement results is attached below.

Referring to your internal manual "Boot Time KPIs" for AM62P, the ROM boot time consumes 30ms and there is a huge gap between TI's measurements and our measurements. I want to know the reason about this and whether we could optimize the boot time KPI during ROM boot. The boot mode we use is OSPI.

BR,

Bomiao