Other Parts Discussed in Thread: C2000WARE

Hi there,

I am using my own IPC message queue library based on the SDK's one (the only difference is that to inicializate the message queue data the cores exchange the address of the put and get buffer just to be safer).

Then when i start to put some stress on my application the CPU1 started to stopped receiving interrupts after some time. I manage to reproduce the error and read the registers on CPU1:

These registers (IPCSTS.IPC1 = 1, PIEIFR.INTx10 = 0) indicate a lack of a Acknolegge action by the CPU1, the others configurations are pretty much the same when is properly working.

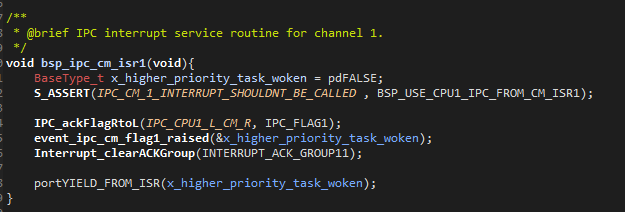

My interrupt code:

I'm acknowledging the flag every interrupt, so i wonder is this problem the result of the interaction of the SET(on the CM side) and ACK(on the CPU1 side) registers when set at the same time? I already tested to clear the flag before setting on the send message to queue function, and it was super effective, but in the SDK's library the function only sets the flag. Is there any documentation about the behaviour of these resgisters?

Best Regards,

Ramon.