Hi

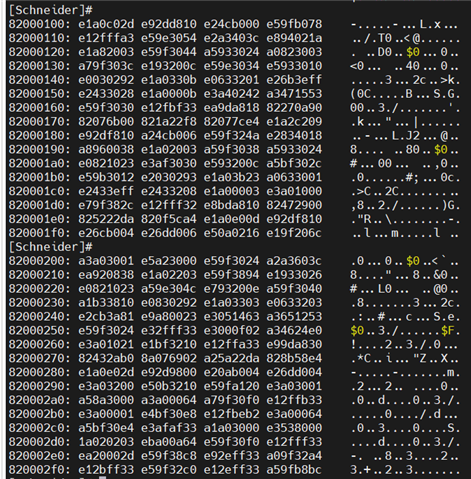

We are using an AM3352 CPU, and the DDR model used is Winbond W632GU6RB-11. Currently, when the system is powered on, we are testing the DDR timing. According to the DDR manufacturer's requirements, the second red box in the following figure requires 500us, but the actual measured time is only 140us, which does not meet the DDR timing requirements and can cause DDR initialization instability. How can we modify the corresponding control time in SPL boot? The base code for the uboot we are currently using is version 201701.

Thanks for your help!