Part Number: AM69A

Other Parts Discussed in Thread: AM67

Hello Experts,

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: AM69A

Other Parts Discussed in Thread: AM67

Hello Experts,

Hi Anthony,

The LED1 pin from the SSD, is supposed to indicate a good status from the SSD, does NOT assert.

That sounds to be an issue. Would be good to know where this power good status LED is connected to.

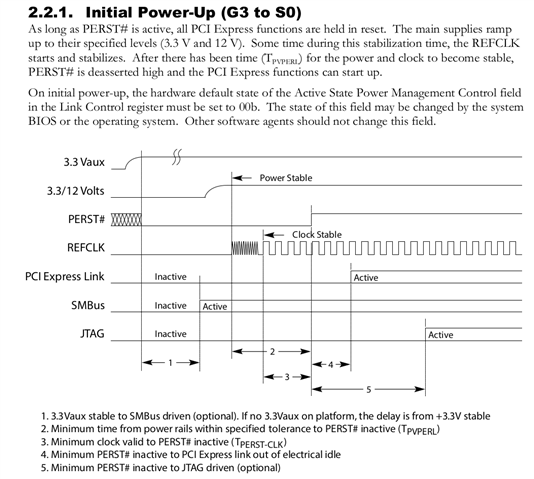

In terms of expectation, we expect the following sequencing for the main signals involved in powering up PCIe. Diagram taken from PCI Express Card Electromechanical Specification Revision 3.0 from the PCI-SIG organization:

From your post, it sounded like the power signal that is part of PCI-SIG specification is monitored, as well as PERST and REFCLK, so I would assume all of these are fine.

What I would instead suspect is that there is an extra power enable pin that is either specific to the SSD or any adapter that is used with the SSD. As an example, there was a "hat" for allowing connection of a M.2 SSD card to a community board by Beagle that used the AM67 SoC. However, the hat itself had an extra PCIE_PWR_EN pin that must be manually asserted for the SSD to get powered. Reference commit: https://openbeagle.org/beagleboard/linux/-/commit/40d9e4d45e92fbae1c52ef8d6637a8cf739bcf89

Perhaps something similar is happening and an extra power enable pin assertion is needed? So, it would be good to know where the power good status LED is connecting to.

Regards,

Takuma