Part Number: AM62A7

Other Parts Discussed in Thread: SYSCONFIG, SK-AM62A-LP

Hi experts,

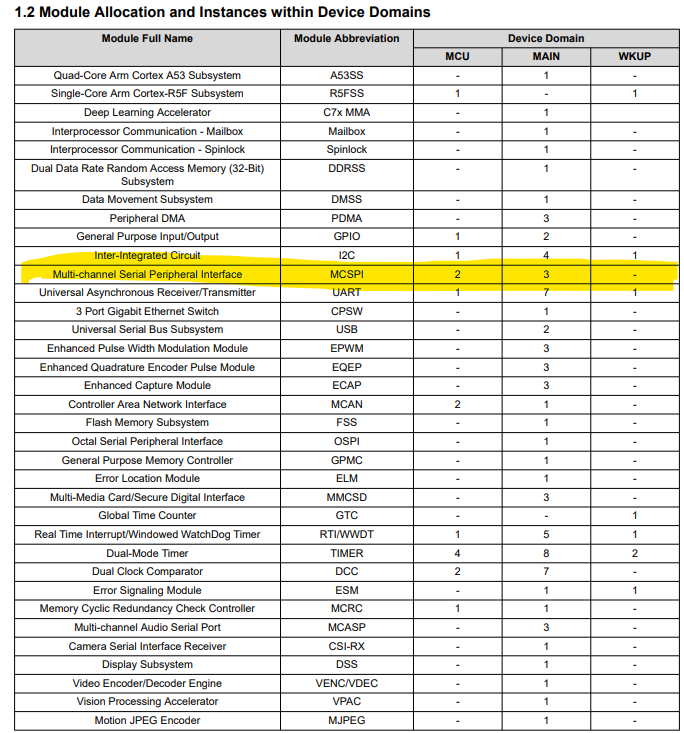

Q:Is my understanding correct that the AM62A's main domain (A53) can control the peripherals of the MCU domain (R5F)?

Specifically, is it correct to say that the main domain (A53) can control a total of 5 SPI interfaces, consisting of 3 main SPI and 2 MCU SPI?

My understand from the following URL that the MCU domain can control some peripherals of the main domain.

AM62Ax MCU+ SDK: Accessing main and wakeup domain peripherals from MCU domain

In MCU+SDK v11.1, I have confirmed that importing "mcspi_loopback_am62ax-sk_a53ss0-0_nortos_gcc-aarch64" and configuring it in SysConfig allows it to build.

Based on TRM section "3.3 Initiator/Target Connectivity," I understand they are internally connected.

Best regards,

O.H