Can UDMA still be applied to C7 core?

I need to do some image copying with DSP, UDMA is faster.

But when I turn on this switch, it will prompt that the channel has failed to open. It doesn't seem to support it.

How should I use it?

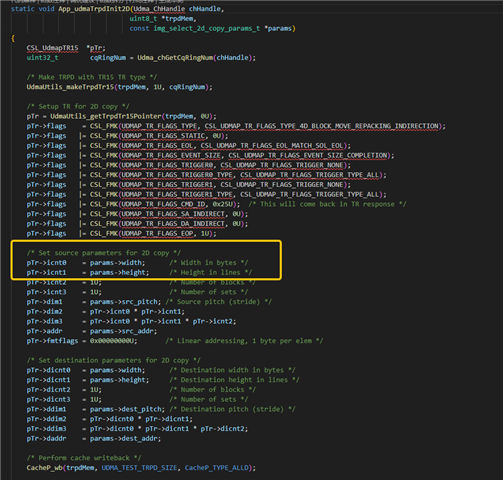

For example, the appUdmaCopy2D interface .

SDK version11.0