Part Number: AM623

Other Parts Discussed in Thread: TPS22965,

Hello,

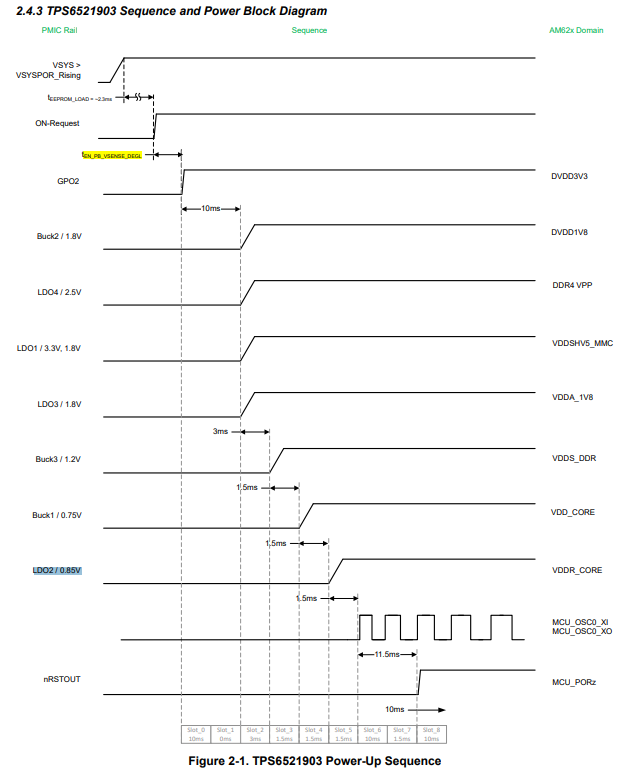

In the reference design, a PMIC (TPS6521903) is used to power sequence and power the AM62x as seen below from the PMIC documentation.

In this power up sequence, the first power supply to come up is the 3.3V from the power switch on top (TPS22965). In the reference design, this 3.3V is used to power peripherals on the dev board which may apply a signal or pull-up GPIO pins on the AM623 before the rest of the power supplies are up. would this cause an issue? should we separate the 3.3V power supply to a 3.3v switched to power peripherals (including the Ethernet PHYs) after VDD_CORE is stable?

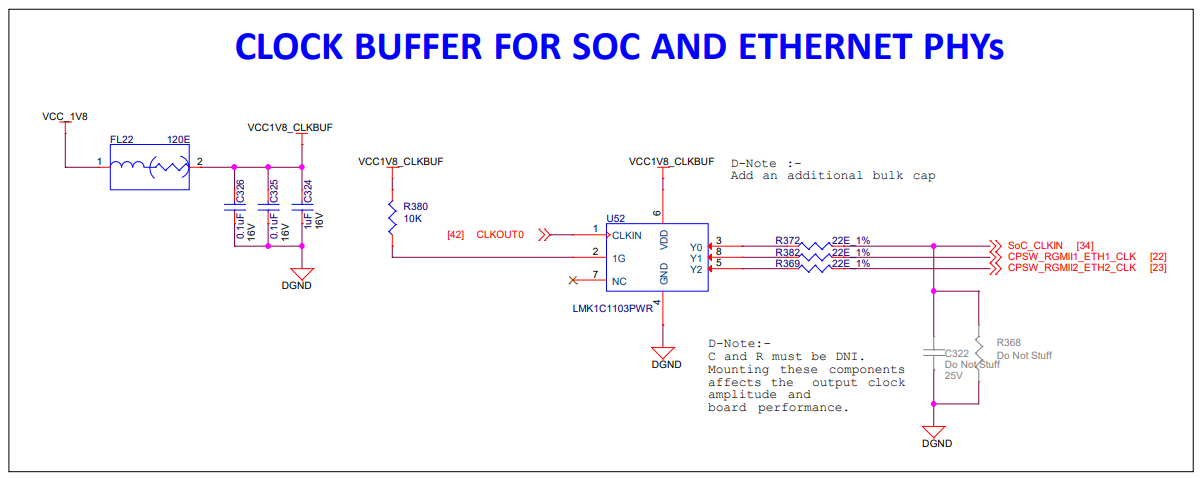

A second question we have about the ref design is for the clock Buffer enable signal shown below,

should this clock be enabled after the LDO2/0.85V in the powerup sequence shown below,

do you see any issues with the buffer being enabled before LDO2 ? should we enable the clock buffer using LDO2?