Dear TI Expert.

We use TDA4VE as our project solution.

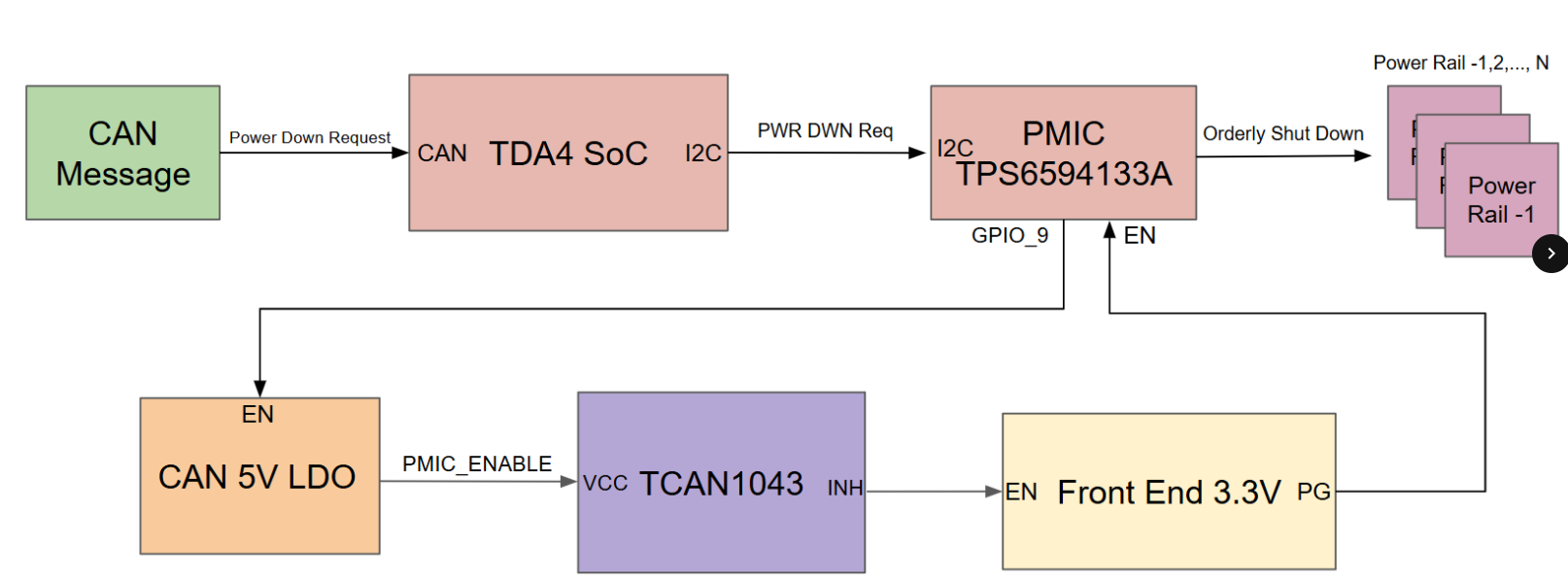

The following is our power-down sequence diagram.

Our ECU has a sleep mode. When SoC execute the sleep command. SoC will shut down the PMIC vias IIC interface to make sure that the SoC Power-down sequence can meet the requirement.

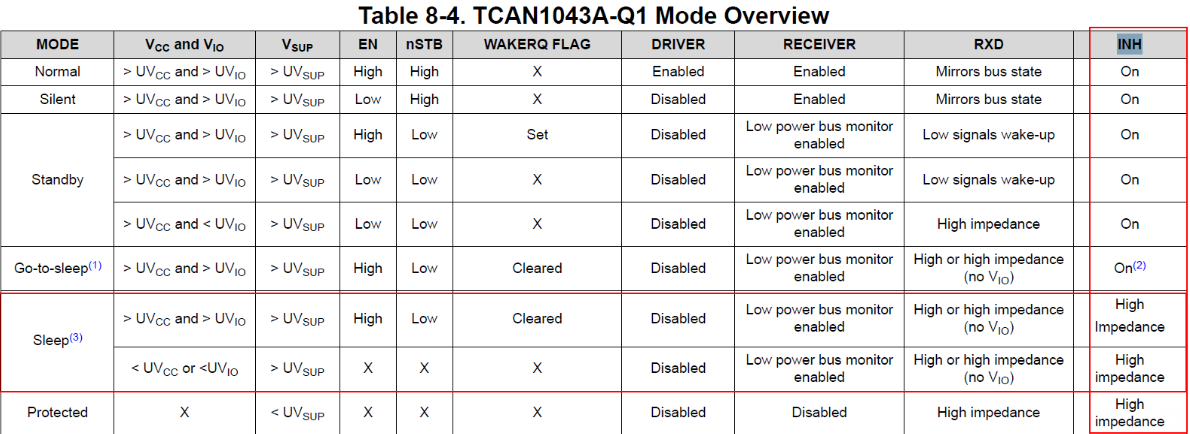

When PMIC fully power down,then GPIO9 will turn low to disable CAN5V LDO. If we disable CAN_5V output, then VCC for TCAN1043A will be zero, so TCAN1043A will be in sleep mode, INH = High Impedance, then Front End 3V3 EN pin is low and disable Sys 3V3 output.

At this point, ECU finish the sleep opeation. When TCAN1043A receive a message from CAN BUS, INH pin will turn to High to reboot Front End 3V3 and then PMIC will reboot too. This is a dormant cycle.

However,there is such a situation that while SoC shut down PMIC vias IIC, if TCAN1043A receive messages from CAN BUS continuously. The PMIC will shut down as expected and INH pin will keep high all the time due to continuous messages from CAN BUS so that Front End 3V3 couldn't reboot.

If Front End 3V3 couldn't reboot, then PMIC can't reboot too. ECU will stuck in sleep mode without control.

Is there any recommendation that we can fix this issue? We can make sure to reboot Front End 3V3 if we want to execute sleep command.

Thanks!