Hello TI Team,

We are facing a power-up issue with TPS6521904 on a custom board and would appreciate your guidance.

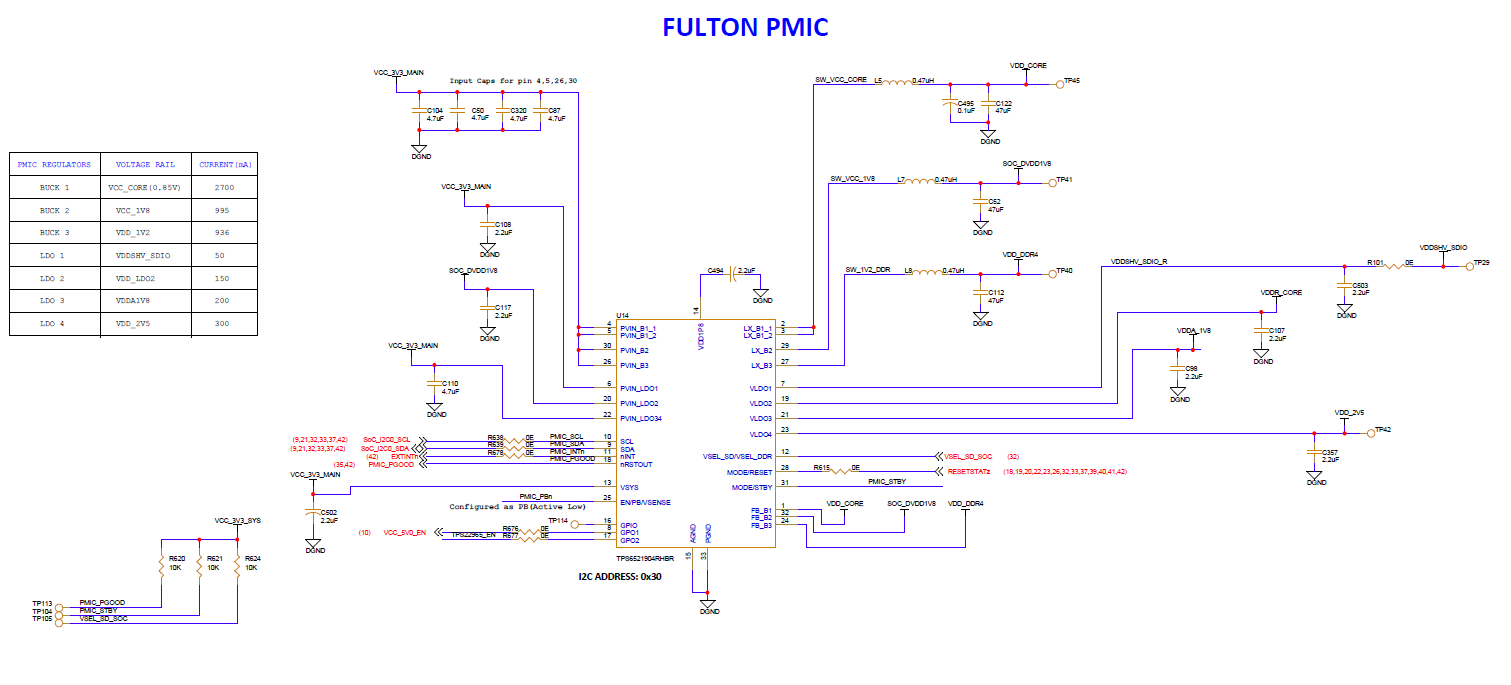

PMIC Details

-

PMIC Variant: TPS6521904RHBR

-

Application: Custom SK-AM62B-P1-based board

-

Input Supply: VCC_MAIN = 3.3 V (verified stable at PMIC input)

-

PMIC Configuration:

-

Using factory TPS6521904RHBR variant

-

Power tree designed strictly as per TI SK-AM62B-P1 reference design

-

Enclosing the snippet of PMIC schematic used in custom board: