Part Number: TDA4VH-Q1

Hello TI,

I'm using J784S4 on SDK 10_01_00_04.

I'm contacting you because I'm facing a problem when using the C7X L2 memory when booting with linux. Indeed I did several tests :

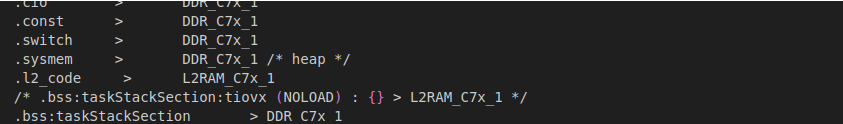

- I tried to create a section in L2 and then use a #pragma to run code in L2 :

![]()

It appears that linux fails to load the binary of the corresponding remoteproc, and the EVM keeps restarting and cannot boot.

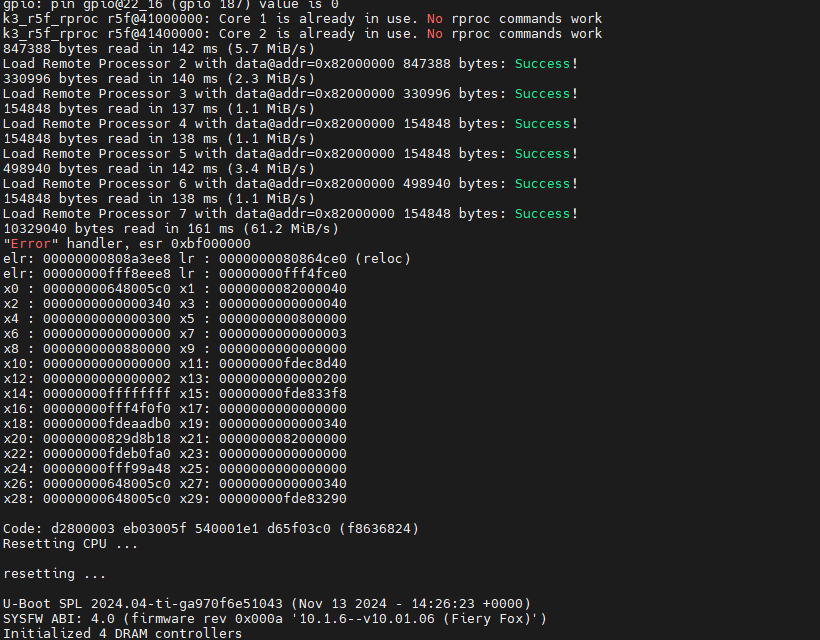

- I tried another method, which use to try to load the binary from u-boot by interrumpting the boot. Here are the steps I followed :

- Copied the app in /run/media/BOOT-mmcblk1p1

- Reboot and interrupt u-boot

- fatls mmc 1:1 (check if the file is here)

- load mmc 1:1 0x90000000 app.bin

- rproc init

- rproc list (get the core id where we want to load the binary)

- rproc load <id> 0x90000000 0x${filesize}

- rproc start <id>

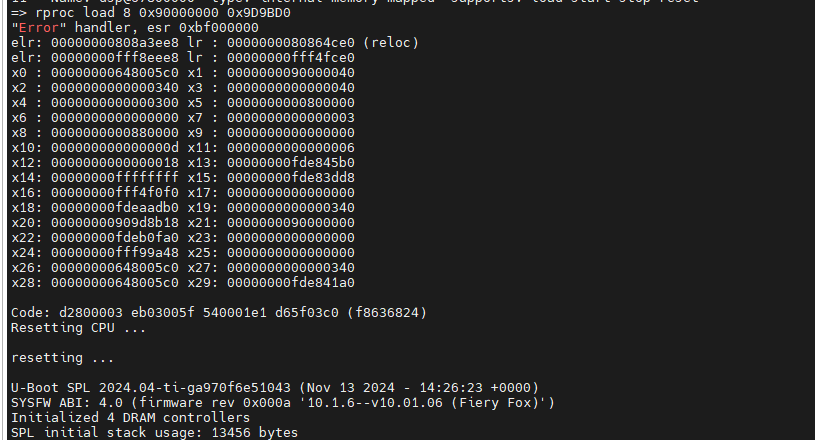

The same problem appears at the load step, the EVM keeps restarting :

- To be sure that the problem comes only when booting with linux, I tried my code in NO_BOOT mode, which means there is no running linux, and I am able to run the code in L2 :

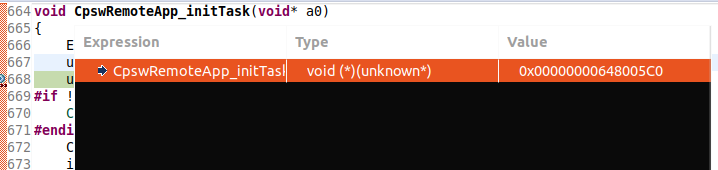

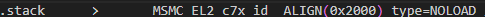

- Also, I noticed that when using L2 for another purpose, for instance to store the section .stack, I cannot use the L2 unless I use the attribute type=NOLOAD in the linker file, knowing that NOLOAD attribute removes the addresses used from this section in the binary :

It appears that there is an issue when trying to load a binary containing L2 usage, and thanks to those tests I expect there is a conflict with A72 core.

It would be great if you can help me on this topic.

Thank you,

Best regards,

Wissam