Part Number: AM2732-Q1

Other Parts Discussed in Thread: AM2732, SYSCONFIG

Hello,

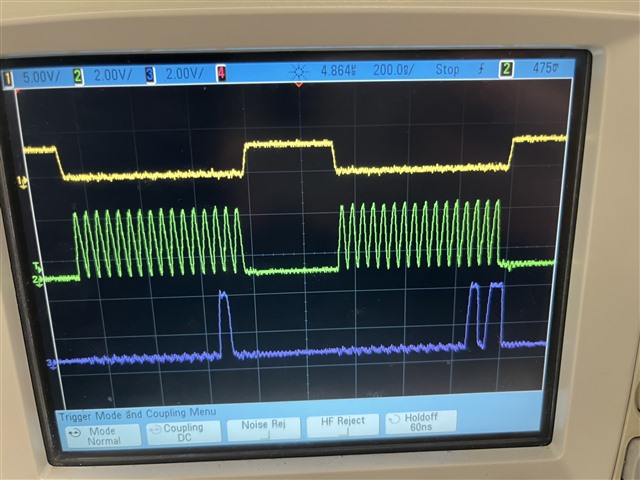

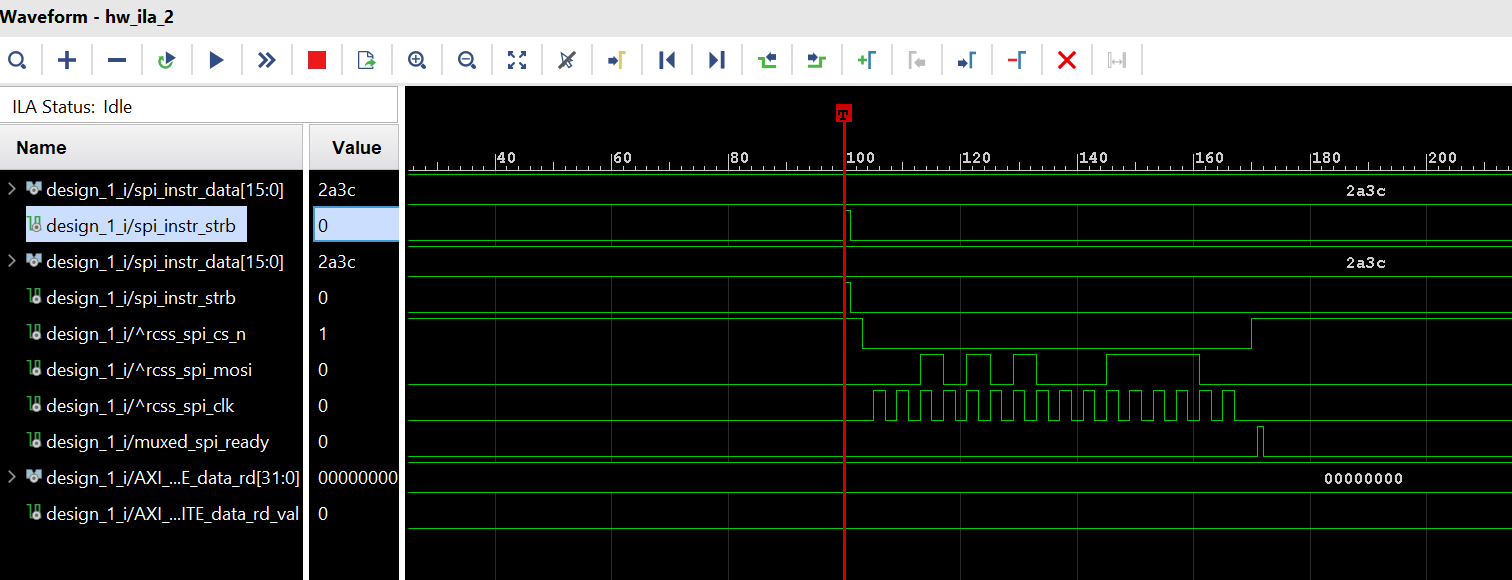

I use the RCSS_SPIA interface as slave in the AM2732 device. The AM2732 device is connected through j1 connector with a FPGA device that sends SPI master frame on RCSS every 10 ms (a simulations of the data send is shown below).

The problem is that in the AM2732 device I only get one interrupt in the beginning with the right data written in memory and then I do not get any more interrupts.

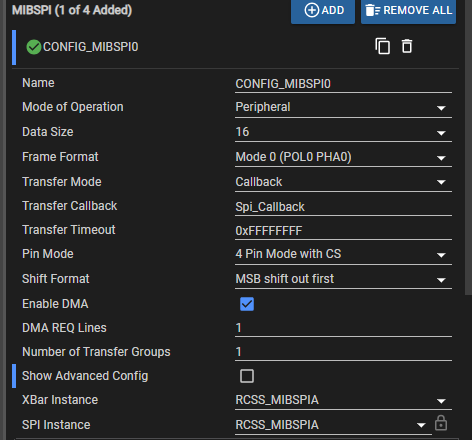

The syscfg and the code used is shown below.

uint32_t intr_callback_cnt = 0;

uint16_t gMibspiRxBuffer[1];

void Spi_Callback(MIBSPI_Handle handle, MIBSPI_Transaction *transaction)

{

CacheP_wbInv(gMibspiRxBuffer, sizeof(gMibspiRxBuffer), CacheP_TYPE_ALLD);

intr_callback_cnt++;

if(intr_callback_cnt == 4){

DebugP_log("4 spi transfers\r\n");

}

}

void spi_slave(void *args)

{

//int32_t status = SystemP_SUCCESS;

uint32_t i;

int32_t transferOK;

MIBSPI_Transaction spiTransaction;

Drivers_open();

Board_driversOpen();

DebugP_log("[MIBSPI] Digital Loopback EDMA example started ...\r\n");

/* Memfill buffers */

for(i = 0U; i < sizeof(gMibspiRxBuffer); i++)

{

gMibspiRxBuffer[i] = 0U;

}

CacheP_wbInv(gMibspiRxBuffer, sizeof(gMibspiRxBuffer), CacheP_TYPE_ALLD);

/* Initiate transfer */

spiTransaction.count = sizeof(gMibspiRxBuffer);

spiTransaction.txBuf = NULL;

spiTransaction.rxBuf = (void *)gMibspiRxBuffer;

spiTransaction.peripheralIndex = 0U;

spiTransaction.arg = NULL;

transferOK = MIBSPI_transfer(gMibspiHandle[CONFIG_MIBSPI0], &spiTransaction);

if((SystemP_SUCCESS != transferOK))

{

DebugP_assert(FALSE); /* MIBSPI transfer failed!! */

}

else

{

DebugP_log("All tests have passed!!\r\n");

}

}Can you tell me whats going wrong?