Other Parts Discussed in Thread: ADS7951, OMAP-L138

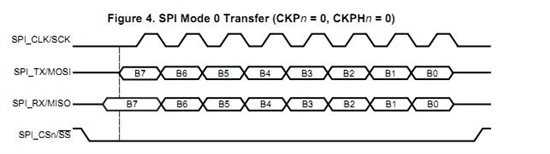

I am trying to understand the operation of the SPI peripheral in the C5515. sprufo3 seems to imply that SPI reads and writes are two different processes. However, most SPI peripherals treat a SPI transaction as both a read *and* a write by clocking data into MISO as it receives data from the master on MOSI. The SPI chip I am interfacing to requires a two-way (read *and* write) transaction since it clocks out status bytes as the C5515 is clocking out commands.

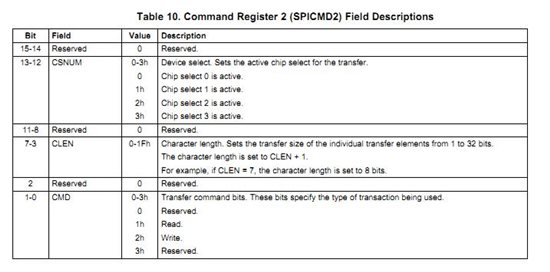

Does the C5515 SPI peripheral indeed perform a bi-directional transfer during a transaction? If so, why does the CSL only support SPI_write and SPI_read functions? After sending a 16-bit transaction to SPIDAT2, will SPIDAT1 have the incoming 16-bit response from my SPI peripheral?