Other Parts Discussed in Thread: OMAP-L132

Hello everybody,

I have serious problems with the series production of our CPU PCB.

We are using the OMAP L138B and the standard boot configuration is 02h.

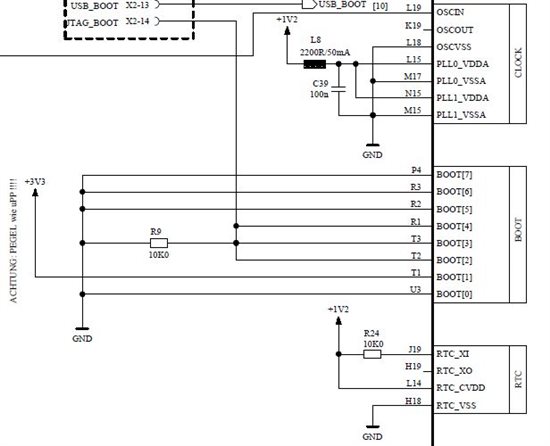

As we als want to boot with the JTAG interface, we connected the pins BOOT[2], BOOT[3], BOOT[4] with an external pulldown resistor to GND,

as shown in the following schematic.

80% of all PCB works fine and there is no start-up / boot problem.

Unfortunately, the remaining 20% has some problems.

The OMAP is stated in a dead-lock loop because it waits for an external emulation debug boot.

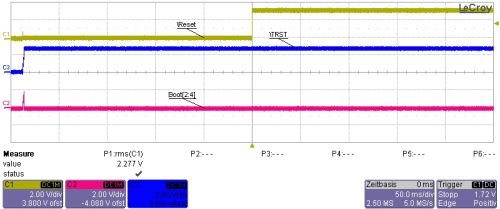

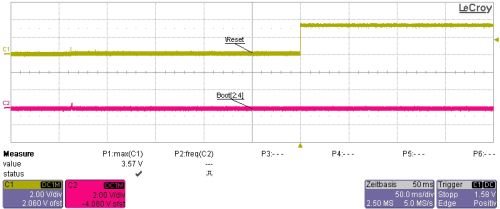

I have recorded the states of the boot pins [2]-[4] and the scope diagramm shows following:

There´s a small glitch 240 ms before the rising edge of the reset. At the time of the rising edge,

the state of the boot pins is low ! Thus, the boot value should be 02h and not 1Eh !

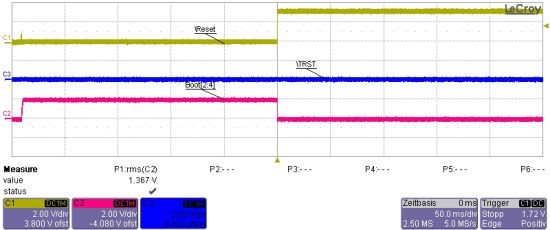

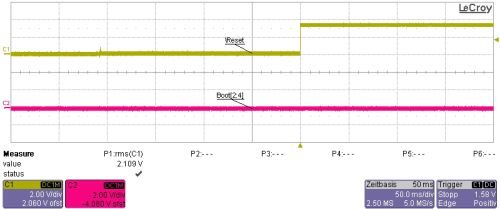

I tried to use a stronger pulldown and change the resistor value to 1k. The result is:

The glitch is smaller than before, but the state at the moment of rising edge is low.

But, compared to the diagramm before, the OMAP starts und is booting !

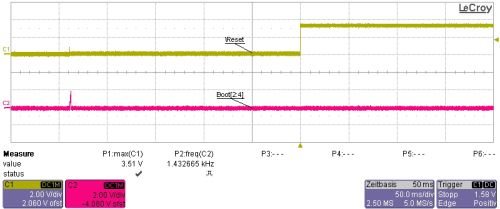

I also compared this states with a PCB which has no problems:

Here, there is no glitch before the rising edge, but the pulldown resistor has still the value of 10k !

Now, I have problems to understand this ! We have no problem to change the resistor value from

10k to 1k... but, is this the solution ? Is there anything else, we don´t know yet ?

According to SPRAD41D.PDF "Using the OMAP-L132/L138 Bootloader", Appendix A the rising edge

of the reset is the master !

"The boot pins are latched by the bootloader when the device exits reset (i.e., on the rising edge of reset)."

At that moment the state of the boot pins are always low and the value of 1Eh should not be latched !

Additional note:

We use an external watchdog which produces a reset after 1.8 s if it is not retriggered by the OMAP,

according to advisory 2.0.20, Errata sheet sprz301e.pdf.

Even after these resets, the OMAP fails to boot. It seems that the correct boot configuration is not newly

latched if the boot configuration is wrong at the first time !

Please, I really need help, cause at the moment our production is stopped !

Thx in advance !

Andreas Amler