Hi,

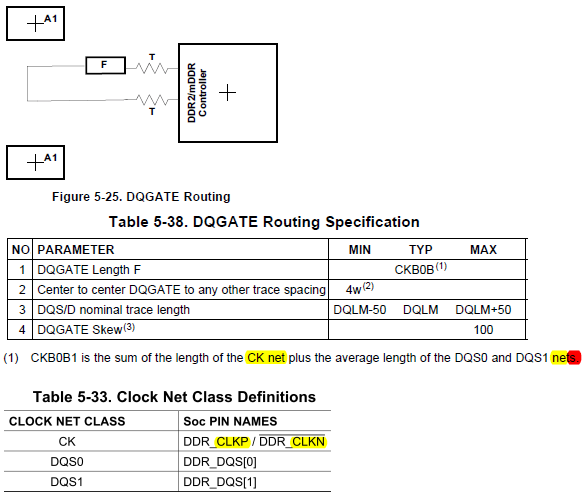

I would like to ask a question with L138 DDR2 controller DQGATE routing.

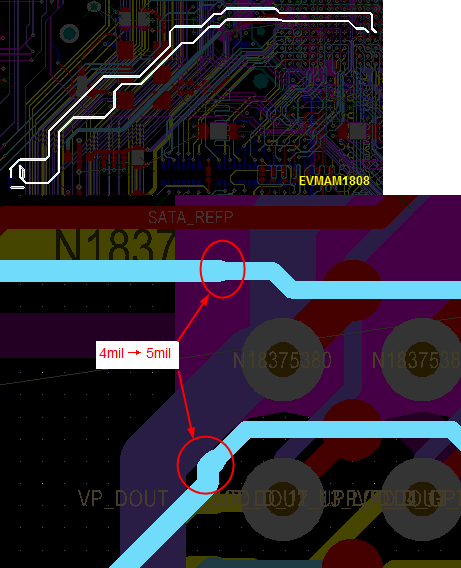

I noticed that there is a trace width 4mil → 5mil change when they go from L138 chip BGA region to outer region.

- There is no specification in L138 datasheet SPRS586C on DQGATE trace width.

- From the viewpoint of signal integrity, non-uniform cross section would certainly cause reflection. Since DQGATE is “DDR2 loopback signal for external DQS gating”, I wonder if it possible that reflection could cause error in the time of the loopback signal.

Could anyone clarify on this?

Zheng