We connected DM8168 with a 800*600 24-bit TFT LCD via LVDS, like the figure below, VOUT[0]_G_Y_YC[2] ~ VOUT[0]_G_Y_YC[9] as Green data bits 0~7, VOUT[0]_B_CB_C[2] ~ VOUT[0]_B_CB_C[9] as Blue bits 0~7, and use PinMux to configure VOUT[0]_R_CR[2]/VOUT[0]_HSYNC/VOUT[1]_Y_YC[2] ~ VOUT[0]_R_CR[9]/VOUT[0]_B_CB_C[1]/VOUT[1]_Y_YC[9] as Red bits 0~7. And the LCD is use DE signal instead of VSYNC and HSYNC to determine the timing.

Runing SDK 5.03, referencing: http://processors.wiki.ti.com/index.php/DM816X_AM389X_VPSS_Video_Driver_User_Guide and do the configuration:

Configure DVO2 VENC:

root@dm816x-evm:~# echo 0 > /sys/devices/platform/vpss/display1/enabled

root@dm816x-evm:~# echo 38362,800/200/24/72,600/24/0/1,1 > /sys/devices/platform/vpss/display1/timings

root@dm816x-evm:~# echo triplediscrete,rgb888 > /sys/devices/platform/vpss/display1/output

root@dm816x-evm:~# echo 1 > /sys/devices/platform/vpss/display1/enabled

switch graphics0(fb0)output from HDMI to DVO2 VENC:

root@dm816x-evm:~# echo 0 > /sys/devices/platform/vpss/graphics0/enabled

root@dm816x-evm:~# echo 1:dvo2 > /sys/devices/platform/vpss/graphics0/nodes

root@dm816x-evm:~# echo 1 > /sys/devices/platform/vpss/graphics0/enabled

then fresh the frame buffer 0:

root@dm816x-evm:~# dd if=/dev/zero of=/dev/fb0 bs=3200 count=600

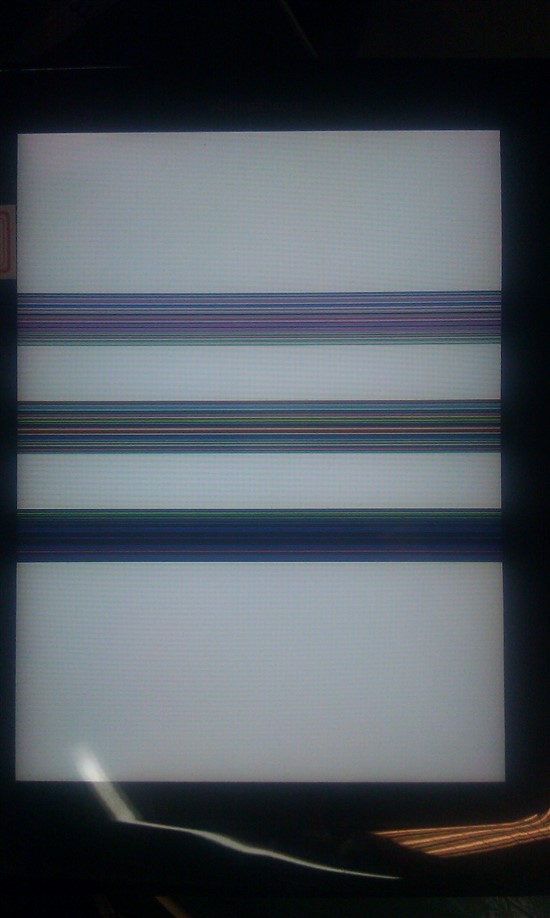

But the LCD panel cannot display anything regular.

I dumped and checked the data of frame buffer, it is correct, and I measured the VOUT[0]_AVID (DE) and VOUT[0]_CLK (pixel clock) signals and the timing is exactly the same as I configured, but all of the LCD data signal (R0~7, G0~7, B0~7) are random and changed, that is said the Vout0 Data is not correct.

Is there anything mistaken or missed when I configure the VPSS driver of DM8168?