Hello,

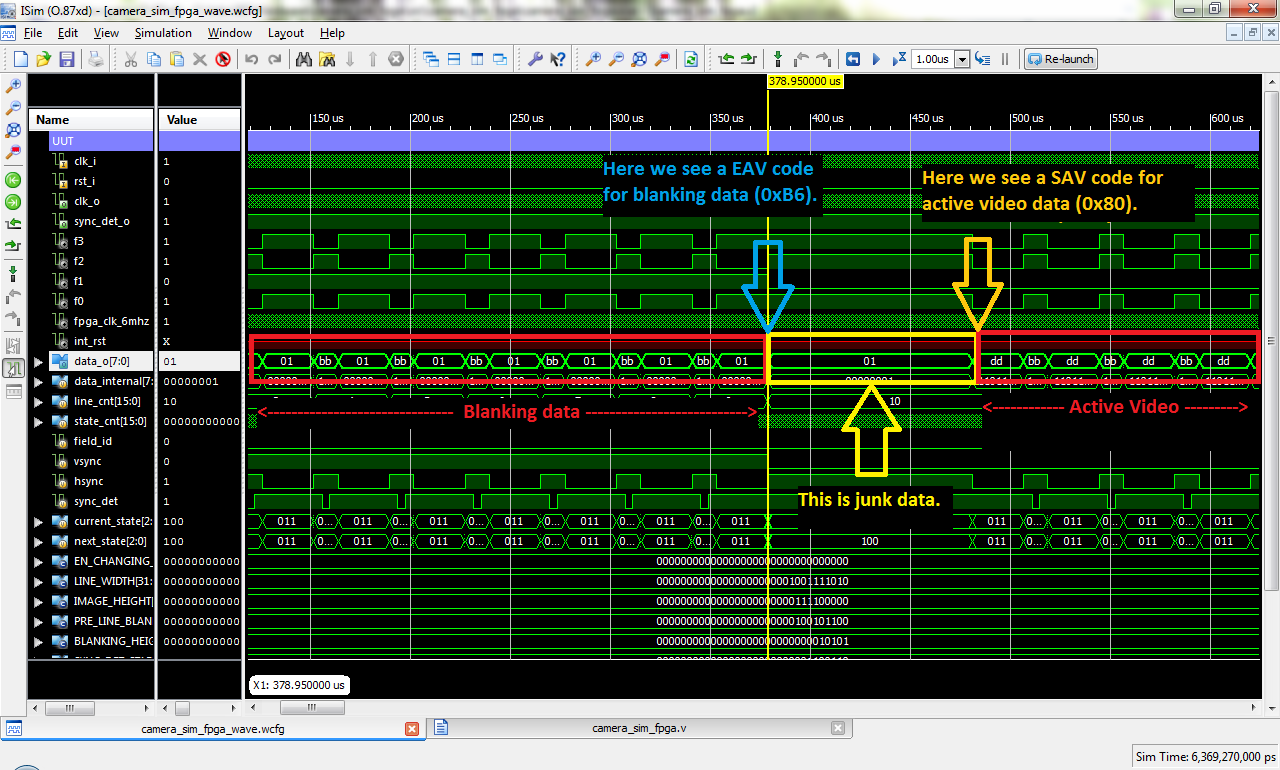

We are trying to get video capture working on a custom TMS320C6A8168 board. We have configured the camera for BT656 at a resolution of 640x480. We have verified the data at VIN1A[7:0] looks like the following:

Bus (VIN1A[7:0]) looks like this:

SAV Valid data EAV

0 1 2 3 4 5 6 7......1276 1277 1278 1279

FF 00 00 80 Y U Y V Y U Y V......Y U Y V FF 00 00 9D

When we try to capture data the system hangs trying to dequeue frames. My guess is that I have not successfully modified ti81xx_fb.c for our configuration. We have made the following changes to our configuration hdvpss_capture_sdev_info

.input_data_format = FVID2_DF_YUV422I_YUYV,

.ctrlChanSel = VPS_VIP_CTRL_CHAN_SEL_7_0,

.video_if_mode = VPS_CAPT_VIDEO_IF_MODE_8BIT,

Question:

1) The video capture system should support this format. I have seen other posts that say it supports this format, but nowhere have I seen the required changes.

2) Do I need to set a new v4l2_dv_preset for this 640x480. If so, what value do I set. If not, do I set it to INVALID and set the correct resolution when I send the ioctl command VIDIOC_S_DV_PRESET.

3) Is there a tool that I can use to dump VIN configuration to see if it is configured correctly?

Thanks,

Craig