Hi

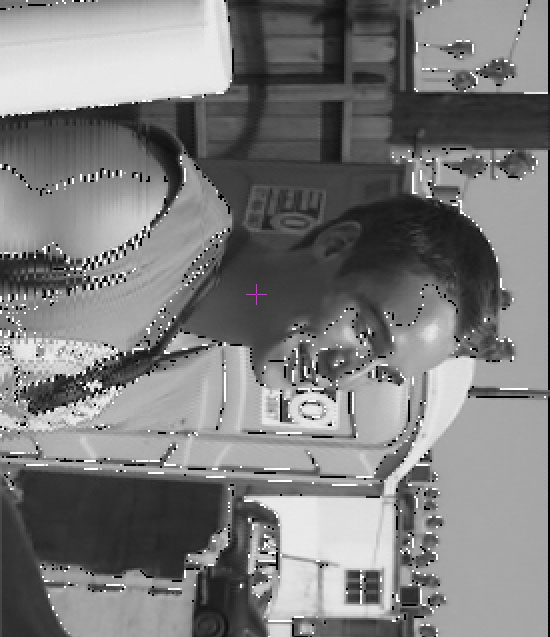

I am using VICP in DM648. resizing video and rotating. (sizing down 0.6)

As you can see in the image below there are artifacts appearing on bright parts of the image and on gray levels borders.

Changing the saturation limits or the qshift does not help.

Can you help please ?

Nissim