Here are is the history of our purchasing:

1 Bought SEED-DEC137 which is based on EVM137 of yours and SDS510 JTAG EMULATOR from SEEDdsp in 2009.

Everything goes fine.

2 Bought a batch of OMAPL137 from ARROWasia in 2011.7, designed our board based on SEED-DEC137.

Our new board pass all the test under CCS3.3(NAND,SDRAM etc), but the board doesn't work in nand mode after reset, and there is no message from UART2.

Our new board pass all the test under CCS3.3(NAND,SDRAM etc), but the board doesn't work in nand mode after reset, and there is no message from UART2.

Here is our analysis:

we find out thae the ROM ID in OMAPL137 of SEED-DEC137 is D800K001, and the ROM ID in OMAPL137 we bought from ARROWasia is D800K003, so maybe the problem comes from chip difference?

Here is the procedures of our boot case:

1 change the OMAPL137 pin to nand flash boot mode

2 we take the same u-boot.out used in SEED-DEC137

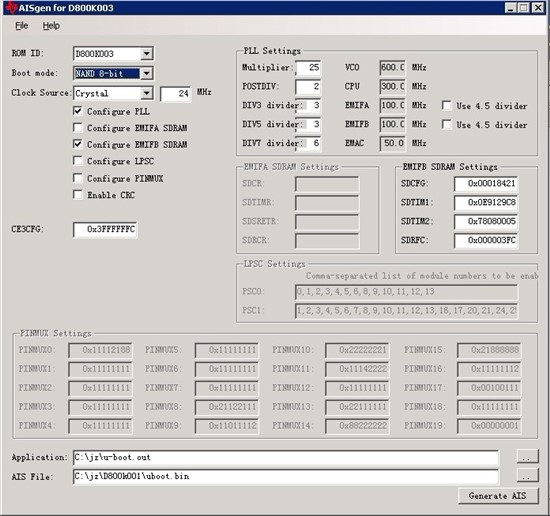

3 take new downloaded AISgen for D800K003 to generate uboot.bin from the u-boot.out

4 take CCS3.3 to load nandwrite project in "OMAP_L137_example" which is used in SEED-DEC137 nand flash burning, burn the uboot.bin into our board.

5 after nandwrite successfully finished burning, quit the CCS3.3, reset the board, nothing happenned, and

2 we take the same u-boot.out used in SEED-DEC137

3 take new downloaded AISgen for D800K003 to generate uboot.bin from the u-boot.out

4 take CCS3.3 to load nandwrite project in "OMAP_L137_example" which is used in SEED-DEC137 nand flash burning, burn the uboot.bin into our board.

5 after nandwrite successfully finished burning, quit the CCS3.3, reset the board, nothing happenned, and

there is no message from UART.

The problem delayed our project for several monthes, so please give us some effective consultation and help.