Hello, I’m using CSL lib in my EDMA design and it works well if I trigger the EDMA manually. My design is based on “edma_interrupt” in the CSL example design. While I trigger the EDAM using the GPIO0, it cannot work.

Here is my work:

chAttr.regionNum = CSL_EDMA3_REGION_1;

chAttr.chaNum = 48; //here I change CSL_EDMA3_CHA_DSP_EVT to 48 (GPIO0)

I also tried to connect GPIO0 and Param set as following:

EDMA3CC_DCHMAP48 = 0x00000020; // map channel 48(tied to gpio0 event) to PaRAM set

I configure GPIO as the following:

GP_DIR |= 0x1; //set the gpio0 as input

GP_BINTEN |= 0x1 ; //enable gpio as souce of interruput

GP_SET_RIS_TRIG |= 0x1 ; //the rising edge of gpio trige the interruput or event

In order to control channel 48, I change the drae(h) as following:s

regionAccess.region = CSL_EDMA3_REGION_1 ;

regionAccess.drae = 0x0000FFFF ;

regionAccess.draeh = 0xFFFF0000 ;

In Xilinx Chipscope, I can see that the GPIO0 works smoothly:

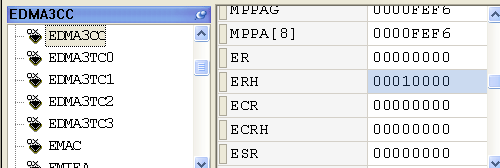

After that, i checked the registers in CCS and found the GPIO0 bit in ERH was set correctly.

So why the EDMA was not triggerred correctly? Can you help me to figure out the mistake in my design