Hi,

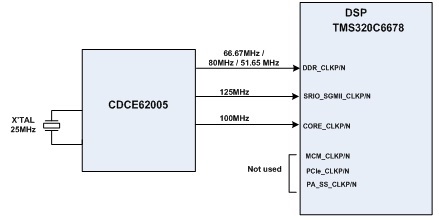

We are using TMS320C6678 DSP in our design. As shown in the below diagram, we are planning to use CDCE62005 and CDCE62002 clock sources for providing the required clocks to the DSP.

Please provide your confirmation and give your comments for any specific considerations on this and on the unused clocks.

Thank you.