Hi everyone

I am running the project C:\ti\pdk_C6678_1_0_0_19\packages\ti\csl\example\edma.and there are some questions for the project.

1,the first example is the pingpong.the project set the srcBuff1[0-255] = 0-255 and srcBuff2[0-255] = 0-255 .when the EDMA has complete

the transfer the detbuff1[0-255] and dstBuff2[0-255] shoule be 0-255.am I right?

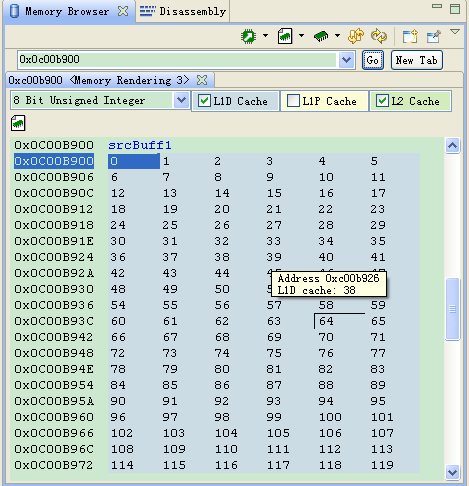

after the initialization of buffer,the memory Browser for the srcBuff1 is like this.

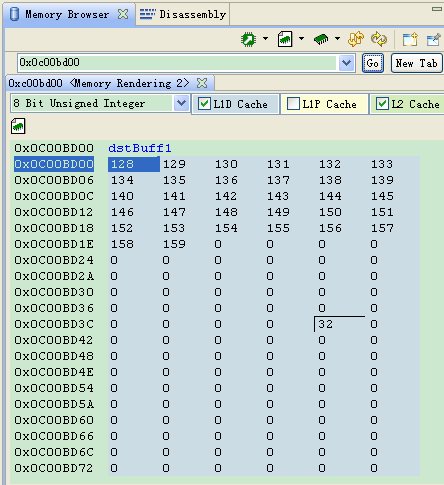

2.but when i set a breakpoint after the completation of EDMA transfer.the dstBuff1 is like this.

why the dstBuffer1 does not equal to srcBuff1?

so I look into the function Verify_Transfer(); I found when code

key = _disable_interrupts();

CACHE_invL1d ((void *)srcBuff, 512, CACHE_WAIT);

CACHE_invL2 ((void *)srcBuff, 512, CACHE_WAIT);

CACHE_invL1d ((void *)dstBuff, 512, CACHE_WAIT);

CACHE_invL2 ((void *)dstBuff, 512, CACHE_WAIT);

_mfence();

/* Re-enable Interrupts. */

_restore_interrupts(key);

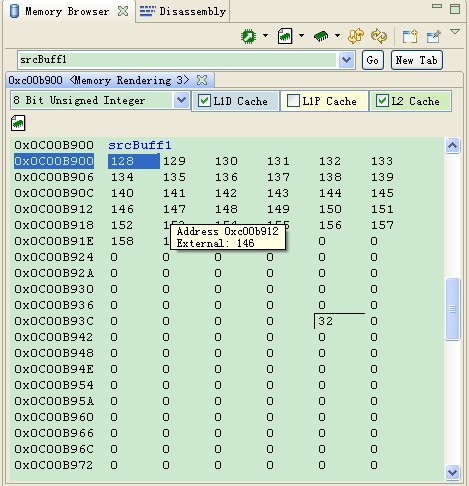

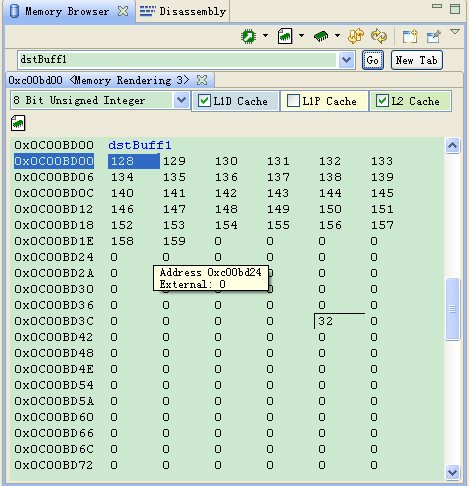

have been implement,the srcBuff1 and dstBuff1 will be like this

what this code used for?why the block in the L1D Cache and L2 should be invalidate?thanks.