Other Parts Discussed in Thread: AM3359

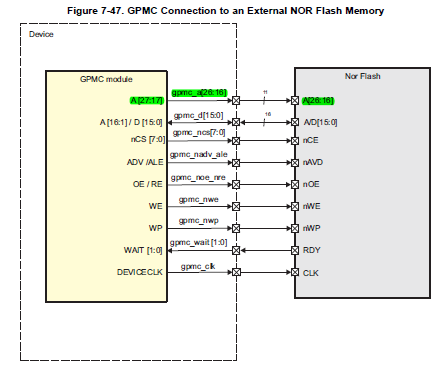

Table 7-5 of the TRM shows GPMC_A[17] connected to A16 of a 16-bit device, GPMC_AD[15] is also shown as connected to A16.

Table 7-52 shows GPMC_A[16] connected to A16 of a 16-bit device.

Which one is correct?

Has anybody implemented a 16-bit NOR FLASH using the multiplexed GPMC_AD[0..15]?

Thanks