Dear All ,

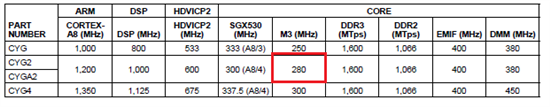

In our custom board we are using the part TMS320DM8168ACYG2(Speed Grade 2). We would like to clock the ARM Cortex A8, DSP , HDVICP2 and HDVPSS to maximum rate supported by the device as listed below :

1) ARM Cortex-A8 – 1.2 GHz

2) C674x DSP – 1 GHz

3) HDVICP2 – 600 MHz

4) HDVPSS – 500 MHz

We would like to know the default clock setting for HDVICP2 clock(SYSCLK3) in PSP 04.04.00.01 uboot. The link (http://processors.wiki.ti.com/index.php/TI81XX_PSP_04.04.00.01_Feature_Performance_Guide) mentions that the HDVICP2 is configured to 600 MHz .

"Clock1 ~= 800MHz, Clock2 ~= 1GHz, Clock3 ~= 600MHz, Clock4 ~= 500 MHz, Clock5 ~= 125MHz"

However when we read the main PLL registers configured in u-boot we found the SYSCLK3 to be configure to 531 MHz. Also in the same link at the end of the document it mentions that SYSCLK3 is configured to 531 MHz

"./sys_clkin_ck/main_pll_clk3_ck/sysclk3_ck/ivahd0_ck/rate ==> 531692931"

Can anyone please confirm what is the clock setting for SYSCLK3 (HDVICP2) of DM8168 on PSP 04.04.00.01 uboot ?

Another important observation is that when we configured the SYSCLK3 clock in uboot to 600 MHz by changing Main PLL FREQ3 registers we observed a reduction in performance of system . The exact behavior was that when we profiled codecs it took more time compared to the earlier setting of 531 MHz. We are not sure why increase in clock resulted in reduction in performance for HDVICP2 module. Does anyone have a clue on what could be going wrong here ?

-Anil