I am trying to bring up a custom board with AM3359 and MT46H64M16LF-6 LPDDR. I am having some issues with data read back.

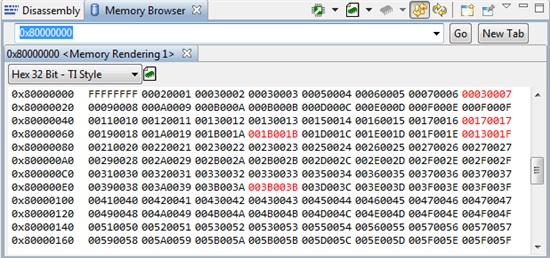

My simple test writes a value to every address (0x00, 0x01, 0x02, etc), and then attempts to read back the value. The lower word for most addresses reads back correctly. The upper word for every memory location reads back as 0x0000.

Every fourth address always reads as a "0x00000000".

If I read the same memory address repeatedly, it does not always return the same value.

I have followed the steps outlined here:

http://processors.wiki.ti.com/index.php/AM335x_EMIF_Configuration_tips

Yet I believe I am still missing something.

Can anyone out there point me in the right direction?

Thank you in advance.