I am working on getting MMU working on AM335x, we have our own custom board (closer design to Beagleboard) with NAND flash

i am able to boot from NAND flash, now i want to use MMU in my code, i am using Codesourcery GCC ver 4.2.3 to compile my own written standalone code

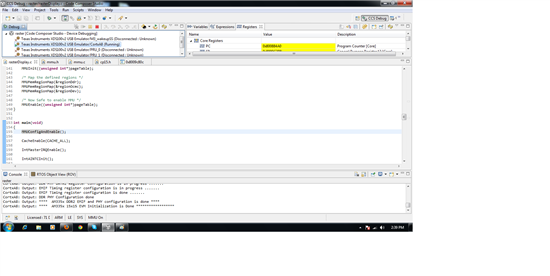

i have used MMU code from Starterware (ver 02.00.00.06) code, but my code stops executing after CP15MMUEnable(); i have used all same code from starterware for MMU, i have verified pageTable address and also verified that entries in pageTable are correct

My code boots from NAND flash, then i copy my initial bootloader to DDR2 RAM at address 0x80000000 and then jump DDR2 for execution, (i want to enable MMU for whole DDR2 memory region) there are certain messages i sent to terminal through UART0, and my code boots up preoperly, but when i try to enable MMU, at CP15MMUEnable, it halts and does not send the characters to terminal after this instruction, am i doing something wrong?

My MMU pageTable address is at 0x83904000 which is 16K boundary aligned as instructed

Below is the code patch i am using to enable MMU, which is taken from starterware code

/*

** Function to setup MMU. This function Maps three regions ( 1. DDR

** 2. OCMC and 3. Device memory) and enables MMU.

*/

void MMUConfigAndEnable(void)

{

/*

** Define DDR memory region of AM335x. DDR can be configured as Normal

** memory with R/W access in user/privileged modes. The cache attributes

** specified here are,

** Inner - Write through, No Write Allocate

** Outer - Write Back, Write Allocate

*/

REGION regionDdr = {

MMU_PGTYPE_SECTION, START_ADDR_DDR, NUM_SECTIONS_DDR,

MMU_MEMTYPE_NORMAL_NON_SHAREABLE(MMU_CACHE_WT_NOWA,

MMU_CACHE_WB_WA),

MMU_REGION_NON_SECURE, MMU_AP_PRV_RW_USR_RW,

(unsigned int*)pageTable

};

/*

** Define OCMC RAM region of AM335x. Same Attributes of DDR region given.

*/

REGION regionOcmc = {

MMU_PGTYPE_SECTION, START_ADDR_OCMC, NUM_SECTIONS_OCMC,

MMU_MEMTYPE_NORMAL_NON_SHAREABLE(MMU_CACHE_WT_NOWA,

MMU_CACHE_WB_WA),

MMU_REGION_NON_SECURE, MMU_AP_PRV_RW_USR_RW,

(unsigned int*)pageTable

};

/*

** Define Device Memory Region. The region between OCMC and DDR is

** configured as device memory, with R/W access in user/privileged modes.

** Also, the region is marked 'Execute Never'.

*/

REGION regionDev = {

MMU_PGTYPE_SECTION, START_ADDR_DEV, NUM_SECTIONS_DEV,

MMU_MEMTYPE_DEVICE_SHAREABLE,

MMU_REGION_NON_SECURE,

MMU_AP_PRV_RW_USR_RW | MMU_SECTION_EXEC_NEVER,

(unsigned int*)pageTable

};

/* Initialize the page table and MMU */

MMUInit((unsigned int*)pageTable);

/* Map the defined regions */

MMUMemRegionMap(®ionDdr);

MMUMemRegionMap(®ionOcmc);

MMUMemRegionMap(®ionDev);

/* Now Safe to enable MMU */

MMUEnable((unsigned int*)pageTable);

}

void MMUInit(unsigned int *masterPt)

{

unsigned int idx;

/* Invalidate the TLB entries */

CP15TlbInvalidate();

/* Set domain access rights */

CP15DomainAccessClientSet();

/* Disable TEX remapping, Access Flag usage and alignment check */

CP15ControlFeatureDisable( CP15_CONTROL_TEXREMAP

| CP15_CONTROL_ACCESSFLAG

| CP15_CONTROL_ALIGN_CHCK

| CP15_CONTROL_MMU);

/* Configure the TTB Control register to use only TTB0 */

CP15TtbCtlTtb0Config();

/* Se the master page table with fault entries */

for(idx = MMU_PAGETABLE_NUM_ENTRY; idx !=0; idx--)

{

*masterPt++ = MMU_PAGETABLE_ENTRY_FAULT;

}

}

void MMUMemRegionMap(REGION *region)

{

unsigned int *ptEntryPtr;

unsigned int ptEntry;

int idx;

/* Get the first entry in the page table to set */

ptEntryPtr = region->masterPtPtr +

(region->startAddr >> MMU_PAGEBOUND_SHIFT);

/* Set the pointer to the last entry */

ptEntryPtr += (region->numPages - 1);

/* Get the start Address MSB 3 nibbles. Ignore extended address */

ptEntry = (region->startAddr & region->pgType) & MMU_PGADDR_MASK;

/*

** Update the page table entry with memory attributes and

** Access Permissions and Security.

** All the regions will be marked as global.

*/

ptEntry |= ((MMU_PGTYPE_MASK & region->pgType)

| region->accsCtrl | region->memAttrib

| region->secureType);

/* Set the entries in the page table for the region attributes */

for(idx = (region->numPages - 1); idx >= 0; idx--)

{

*ptEntryPtr-- = ptEntry + (idx << MMU_PAGEBOUND_SHIFT) ;

}

}

void MMUEnable(unsigned int *masterPt)

{

/* Set TTB0 register */

CP15Ttb0Set((unsigned int)masterPt);

/* Enable MMU */

CP15MMUEnable();

}

Please help !!!